MC9S08DZ16 FREESCALE [Freescale Semiconductor, Inc], MC9S08DZ16 Datasheet - Page 402

MC9S08DZ16

Manufacturer Part Number

MC9S08DZ16

Description

8-Bit HCS08 Central Processor Unit (CPU)

Manufacturer

FREESCALE [Freescale Semiconductor, Inc]

Datasheet

1.MC9S08DZ16.pdf

(416 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08DZ16ACLC

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S08DZ16ACLF

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 402 of 416

- Download datasheet (5Mb)

Appendix B Timer Pulse-Width Modulator (TPMV2)

the value in the TPMxCNTH:TPMxCNTL counter is 0x0000. (The new duty cycle does not take effect

until the next full period.)

B.3.3

This type of PWM output uses the up-/down-counting mode of the timer counter (CPWMS = 1). The

output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM

signal and the period is determined by the value in TPMxMODH:TPMxMODL.

TPMxMODH:TPMxMODL should be kept in the range of 0x0001 to 0x7FFF because values outside this

range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

If the channel value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will

be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (nonzero)

modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This

implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if

generation of 100% duty cycle is not necessary). This is not a significant limitation because the resulting

period is much longer than required for normal applications.

TPMxMODH:TPMxMODL = 0x0000 is a special case that should not be used with center-aligned PWM

mode. When CPWMS = 0, this case corresponds to the counter running free from 0x0000 through

0xFFFF, but when CPWMS = 1 the counter needs a valid match to the modulus register somewhere other

than at 0x0000 in order to change directions from up-counting to down-counting.

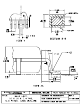

Figure B-11

determines the pulse width (duty cycle) of the CPWM signal. If ELSnA = 0, the compare match while

counting up forces the CPWM output signal low and a compare match while counting down forces the

output high. The counter counts up until it reaches the modulo setting in TPMxMODH:TPMxMODL, then

counts down until it reaches zero. This sets the period equal to two times TPMxMODH:TPMxMODL.

Center-aligned PWM outputs typically produce less noise than edge-aligned PWMs because fewer I/O pin

transitions are lined up at the same system clock edge. This type of PWM is also required for some types

of motor drives.

402

Center-Aligned PWM Mode

shows the output compare value in the TPM channel registers (multiplied by 2), which

TPMxMODH:TPMx

TPM1C

COUNT =

Figure B-11. CPWM Period and Pulse Width (ELSnA = 0)

pulse width = 2 x (TPMxCnVH:TPMxCnVL)

period = 2 x (TPMxMODH:TPMxMODL);

MC9S08DZ60 Series Data Sheet, Rev. 4

for TPMxMODH:TPMxMODL = 0x0001–0x7FFF

(COUNT DOWN)

COMPARE

OUTPUT

2 x

2 x

PULSE WIDTH

COUNT = 0

PERIOD

(COUNT UP)

COMPARE

OUTPUT

TPMxMODH:TPMx

COUNT =

Freescale Semiconductor

Eqn. 17-1

Eqn. 17-2

Related parts for MC9S08DZ16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: