MC9S08DZ16 FREESCALE [Freescale Semiconductor, Inc], MC9S08DZ16 Datasheet - Page 157

MC9S08DZ16

Manufacturer Part Number

MC9S08DZ16

Description

8-Bit HCS08 Central Processor Unit (CPU)

Manufacturer

FREESCALE [Freescale Semiconductor, Inc]

Datasheet

1.MC9S08DZ16.pdf

(416 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08DZ16ACLC

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC9S08DZ16ACLF

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 157 of 416

- Download datasheet (5Mb)

8.5.2.2

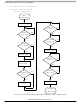

In this example, the MCG will move through the proper operational modes from PEE mode with a 4 MHz

crystal configured for an 8 MHz bus frequency (see previous example) to BLPI mode with a 16 kHz bus

frequency.First, the code sequence will be described. Then a flowchart will be included which illustrates

the sequence.

Freescale Semiconductor

1. First, PEE must transition to PBE mode:

2. Then, PBE must transition either directly to FBE mode or first through BLPE mode and then to

3. Next, FBE mode transitions into FBI mode:

a) MCGC1 = 0x90 (%10010000)

b) Loop until CLKST (bits 3 and 2) in MCGSC are %10, indicating that the external reference

FBE mode:

a) BLPE: If a transition through BLPE mode is desired, first set LP (bit 3) in MCGC2 to 1

b) BLPE/FBE: MCGC1 = 0xB8 (%10111000)

c) BLPE/FBE: MCGC3 = 0x04 (%00000100)

d) BLPE: If transitioning through BLPE mode, clear LP (bit 3) in MCGC2 to 0 here to switch to

e) FBE: Loop until PLLST (bit 5) in MCGSC is clear, indicating that the current source for the

f) FBE: Optionally, loop until LOCK (bit 6) in the MCGSC is set, indicating that the FLL has

a) MCGC1 = 0x44 (%01000100)

b) Loop until IREFST (bit 4) in MCGSC is 1, indicating the internal reference clock has been

c) Loop until CLKST (bits 3 and 2) in MCGSC are %01, indicating that the internal reference

– CLKS (bits 7 and 6) set to %10 in order to switch the system clock source to the external

clock is selected to feed MCGOUT

– RDIV (bits 5-3) set to %111, or divide-by-128 because 4 MHz / 128 = 31.25 kHz which is

– PLLS (bit 6) clear to 0 to select the FLL. In BLPE mode, changing this bit only prepares the

FBE mode

PLLS clock is the FLL

acquired lock. Although the FLL is bypassed in FBE mode, it is still enabled and running.

– CLKS (bits7 and 6) in MCGSC1 set to %01 in order to switch the system clock to the

– IREFS (bit 2) set to 1 to select the internal reference clock as the reference clock source

– RDIV (bits 5-3) set to %000, or divide-by-1 because the trimmed internal reference should

selected as the reference clock source

clock is selected to feed MCGOUT

Example # 2: Moving from PEE to BLPI Mode: External Crystal = 4 MHz,

Bus Frequency =16 kHz

reference clock

in the 31.25 kHz to 39.0625 kHz range required by the FLL. In BLPE mode, the

configuration of the RDIV does not matter because both the FLL and PLL are disabled.

Changing them only sets up the dividers for FLL usage in FBE mode

MCG for FLL usage in FBE mode. With PLLS = 0, the VDIV value does not matter.

internal reference clock

be within the 31.25 kHz to 39.0625 kHz range required by the FLL

MC9S08DZ60 Series Data Sheet, Rev. 4

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

157

Related parts for MC9S08DZ16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: