XE8000EV108 Semtech, XE8000EV108 Datasheet - Page 113

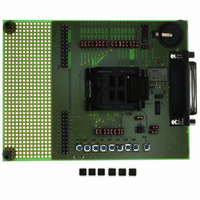

XE8000EV108

Manufacturer Part Number

XE8000EV108

Description

EVAL BOARD FOR XE8806/XE8807

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV108

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC06AMI026

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 113 of 143

- Download datasheet (889Kb)

write to RegUartTx

write to RegUartTx

15.8.3

On detection of the start bit, the UartRxBusy bit is set. On detection of the stop bit, the received data are

transferred from the internal shift register to the register RegUartRx. At the same time, the UartRxFull bit is set

and an interrupt is generated on Irq_uart_Rx. This indicates that new data is available in RegUartRx. The timing

diagram is shown in Figure 15-2.

The UartRxFull bit is cleared when RegUartRx is read. If the register was not read before the receiver transfers a

new word to it, the bit UartRxOErr (overflow error) is set and the previous contents of the register are lost.

UartRxOErr is cleared by writing any data to RegUartRxSta.

The bit UartRxSErr is set if a start error has been detected. The bit is updated at data transfer to RegUartRx.

The bit UartRxPErr is set if a parity error has been detected, i.e. the received parity bit is not equal to the

calculated parity of the received data. The bit is updated at data transfer to RegUartRx.

The bit UartRxFErr in RegUartRxSta shows that a frame error has been detected. No stop bit has been detected.

© Semtech 2006

Asynchronous Transmission

Asynchronous Transmission (back to back)

reguarttx_shift

reguarttx_shift

UartTxBusy

UartTxBusy

RegUartTx

Irq_uart_Tx

RegUartTx

Irq_uart_Tx

UartTxFull

UartTxFull

shift clock

shift clock

Reception

Tx

Tx

word 1

word 1

word 1

start

word 2

word 1

start

word 2

Figure 15-1. UART transmission timing diagram.

word 1

b0

b0

b1

15-6

b6/7

stop

b6/7

word 2

start

parity

XE8806A/XE8807A

stop

www.semtech.com

Related parts for XE8000EV108

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: