XE8000EV108 Semtech, XE8000EV108 Datasheet - Page 119

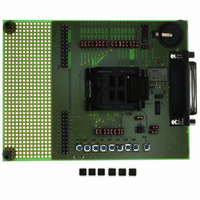

XE8000EV108

Manufacturer Part Number

XE8000EV108

Description

EVAL BOARD FOR XE8806/XE8807

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV108

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC06AMI026

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 119 of 143

- Download datasheet (889Kb)

16.4 Interrupts map

16.5 Conditional edge detection 1

Condition 1 is satisfied when S0=1 at the falling edge of S1. The bit UsrtCond1 in RegUsrtCond1 is set when the

condition 1 is detected and the USRT interface is enabled (UsrtEnable=1). Condition 1 is asserted for both modes

(receiver and transmitter). The UsrtCond1 bit is read only and is cleared by all reset conditions and by writing any

data to its address.

Condition 1 occurrence also generates an interrupt on Irq_cond1.

16.6 Conditional edge detection 2

Condition 2 is satisfied when S0=1 at the rising edge of S1. The bit UsrtCond2 in RegUsrtCond2 is set when the

condition 2 is detected and the USRT interface is enabled. Condition 2 is asserted for both modes (receiver and

transmitter). The UsrtCond2 bit is read only and is cleared by all reset conditions and by writing any data to its

address.

Condition 2 occurrence also generates an interrupt on Irq_cond2.

© Semtech 2006

S1

S0

S1

S0

Irq_cond2

Irq_cond1

interrupt source

Table 16-9: Interrupts map

RegIrqMid(7)

RegIrqMid(6)

Figure 16-1: Condition 1

Figure 16-2: Condition 2

default mapping in the interrupt manager

16-4

XE8806A/XE8807A

www.semtech.com

Related parts for XE8000EV108

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: