XE8000EV108 Semtech, XE8000EV108 Datasheet - Page 55

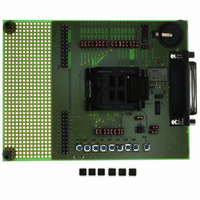

XE8000EV108

Manufacturer Part Number

XE8000EV108

Description

EVAL BOARD FOR XE8806/XE8807

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV108

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC06AMI026

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 55 of 143

- Download datasheet (889Kb)

Once memorized, an interrupt flag can be cleared by writing a ‘1’ in the corresponding bit of RegIrqHig, RegIrqMid

or RegIrqLow. Writing a ‘0’ does not modify the flag. To definitively clear the interrupt, one has to clear the

CoolRISC interrupt in the CoolRISC stat register. All interrupts are automatically cleared after a reset.

Two registers are provided to facilitate the writing of interrupt service software. RegIrqPriority contains the number

of the highest priority set (its value is 0xFF when no interrupt is memorized). RegIrqIrq indicates the priority level of

the currently activated interrupts.

All interrupt sources are sampled by the highest frequency in the system. A CPU interruption is generated and

memorized when an interrupt becomes high. Between the rising edge of the interrupt on the peripheral and the

rising edge on the CoolRISC core, there is a latency of one clock cycle.

8.5

This chapter describes an example of the software used for the interrupt handler. This software is present by

default in the software development environments. It represents only one of several possible ways of handling the

interrupts.

© Semtech 2006

Interrupt handling software

RegIrqHig

RegIrqEnHig

stat

IE2

7

7

Figure 8-1. Principle of the interrupt handler.

IE1

6

6

GIE

5

5

RegIrqLow RegIrqMid

IN2

8-5

…

4

4

IN1

3

…

3

IN0

2

2

EV1

1

1

XE8806A/XE8807A

EV0

0

0

www.semtech.com

Related parts for XE8000EV108

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: