XE8000EV108 Semtech, XE8000EV108 Datasheet - Page 75

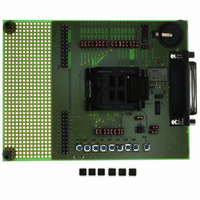

XE8000EV108

Manufacturer Part Number

XE8000EV108

Description

EVAL BOARD FOR XE8806/XE8807

Manufacturer

Semtech

Type

MCUr

Specifications of XE8000EV108

Contents

Fully Assembled Evaluation Board

For Use With/related Products

XE88LC06AMI026

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

- Current page: 75 of 143

- Download datasheet (889Kb)

The timing of the CPU clock (Figure 12-2) depends on the selection of the CpuSel bit in the RegSysClock register

and is given in Table 12-11. f

the 32 kHz depends on the selected clock source (see clock block documentation).

Pins PB[5] and PB[4] can be used for S1 and S0 of the USRT (see USRT documentation) when the UsrtEnable bit

is set in RegUsrtCtrl. The PB[5] and PB[4] then become open-drain. This overrides the values contained in

PBOpen(5:4), PBOut(5:4) and PBDir(5:4). If there is no external pull-up resistor on these pins, internal pull-ups

should be selected by setting PBPullup(5:4). When S0 is an output, the pin PB[4] takes the value of UsrtS0 in

RegUsrtS0. When S1 is an output, the pin PB[5] takes the value of UsrtS1 in RegUsrtS1.

Pins PB[6] and PB[7] can be used by the UART (see UART documentation). When UartEnTx in RegUartCtrl is set

to 1, PB[6] is used as output signal Tx. When UartEnRx in RegUartCtrl is set to 1, PB[7] is used as input signal

Rx. This overrides the values contained in PBOut(7:6) and PBDir(7:6).

12.7 Port B digital capabilities

12.7.1

The direction of each bit within Port B (input only or input/output) can be individually set using the RegPBDir

register. If PBDir[x] = 1, both the input and output buffer are active on the corresponding Port B. If PBDir[x] = 0,

the corresponding Port B pin is an input only and the output buffer is in high impedance. After reset (nresetpconf)

Port B is in input only mode (PBDir[x] are reset to 0).

The input values of Port B are available in RegPBIn (read only). Reading is always direct - there is no debounce

function in Port B. In case of possible noise on input signals, a software debouncer with polling or an external

hardware filter have to be realized. The input buffer is also active when the port is defined as output and the

effective value on the pin can be read back.

Data stored in RegPBOut are outputted at Port B if PBDir[x] is 1. The default values after reset is low (0).

When a pin is in output mode (PBDir[x] is set to 1), the output can be a conventional CMOS (Push-Pull) or a N-

channel Open-drain, driving the output only low. By default, after reset (nresetpconf) the PBOpen[x] in

RegPBOpen is cleared to 0 (push-pull). If PBOpen[x] in RegPBOpen is set to 1 then the internal P transistor in

the output buffer is electrically removed and the output can only be driven low (PBOut[x]=0). When PBOut[x]=1,

the pin is high Impedance. The internal pull-up or an external pull-up resistor can be used to drive to pin high.

Note: Because the P transistor actually exists (this is not a real Open-drain output) the pull-up range is limited to

Each bit can be set individually for pull-up or not using register RegPBPullup. Input is pulled up when its

corresponding bit in this register is set to 1. Default status after (nresetpconf) is 1, which means with pull up. To

limit power consumption, pull-up resistors are only enabled when the associated pin is either a digital input or an N-

channel open-drain output with the pad set to 1. In the other cases (push-pull output or open-drain output driven

low), the pull up resistors are disabled independent of the value in RegPBPullup.

After power-on reset, the Port B is configured as an input port with pull-up. During power-on reset (see reset block

documentation) however, the pin PB[1] is pulled down in stead of pulled up. Once the power-on reset completed,

the pin PB[1] is pulled up, exactly as the other Port B pins.

© Semtech 2006

VDD + 0.2V (avoid forward bias the P transistor / diode).

Port B digital configuration

max

is the frequency of fastest clock present in the circuit. Note that the tolerance on

Table 12-11. CPU clock timing parameters.

CpuSel

0

1

f1

f

f

max

max

12-6

/4

f2

f

32 kHz

max

XE8806A/XE8807A

www.semtech.com

Related parts for XE8000EV108

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

EVALUATION BOARD

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

VOLTAGE SUPPRESSOR, TRANSIENT SEMTECH

Manufacturer:

Semtech

Datasheet:

Part Number:

Description:

HIGH VOLTAGE CAPACITORS MONOLITHIC CERAMIC TYPE

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

EZ1084CM5.0 AMP POSITIVE VOLTAGE REGULATOR

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

3.0 AMP LOW DROPOUT POSITIVE VOLTAGE REGULATORS

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

RailClamp Low Capacitance TVS Diode Array

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Semtech Corporation

Datasheet: