KMSC7119VM1200 Freescale Semiconductor, KMSC7119VM1200 Datasheet - Page 38

KMSC7119VM1200

Manufacturer Part Number

KMSC7119VM1200

Description

DSP 16BIT W/DDR CTRLR 400-MAPBGA

Manufacturer

Freescale Semiconductor

Series

MSC711x StarCorer

Type

Fixed Pointr

Datasheet

1.MSC7119VF1200.pdf

(60 pages)

Specifications of KMSC7119VM1200

Interface

Host Interface, I²C, UART

Clock Rate

300MHz

Non-volatile Memory

ROM (8 kB)

On-chip Ram

464kB

Voltage - I/o

3.30V

Voltage - Core

1.20V

Operating Temperature

-40°C ~ 105°C

Mounting Type

*

Package / Case

400-MAPBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KMSC7119VM1200

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

2.5.11

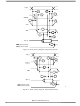

Figure 24 shows the signal behavior of the EVNT pins.

2.5.12

Figure 25 shows the signal behavior of the

38

Notes:

Notes:

Number

Number

601

602

603

604

67

68

1.

2.

3.

1.

2.

3.

4.

5.

6.

Event Timing

GPIO Timing

Refer to Table 27 for a definition of the APBCLK period.

Direction of the EVNT signal is configured through the GPIO and Event port registers.

Refer to the signal chapter in the MSC711x Reference Manual for details on EVNT pin functionality.

Refer to Table 27 for a definition of the APBCLK period.

Direction of the GPIO signal is configured through the GPIO port registers.

Refer to Section 1.5 for details on GPIO pin functionality.

GPI data is synchronized to the APBCLK internally and the minimum listed is the capability of the hardware to capture data

into a register when the GPADR is read. The specification is not tested due to the asynchronous nature of the input and

dependence on the state of the DSP core. It is guaranteed by design.

The output signals cannot toggle faster than 75 MHz.

Level-sensitive interrupts should be held low until the system determines (via the service routine) that the interrupt is

acknowledged.

EVNT as input

EVNT as output

GPI

GPO

Port A edge-sensitive interrupt

Port A level-sensitive interrupt

4.5

5

Characteristics

Characteristics

EVNT out

EVNT in

GPO

GPI

Table 30. GPIO Signal Timing

GPI/GPO

Figure 25. GPI/GPO Pin Timing

Table 29. EVNT Signal Timing

Figure 24. EVNT Pin Timing

MSC7119 Data Sheet, Rev. 8

pins.

Synchronous to core clock

Synchronous to core clock

Asynchronous

Asynchronous

Asynchronous

Asynchronous

Type

Type

1,2,3

602

601

68

67

1.5 × APBCLK periods

1.5 × APBCLK periods

1.5 × APBCLK periods

3 × APBCLK periods

Freescale Semiconductor

1 APBCLK period

1 APBCLK period

Min

Min

6