KMSC7119VM1200 Freescale Semiconductor, KMSC7119VM1200 Datasheet - Page 39

KMSC7119VM1200

Manufacturer Part Number

KMSC7119VM1200

Description

DSP 16BIT W/DDR CTRLR 400-MAPBGA

Manufacturer

Freescale Semiconductor

Series

MSC711x StarCorer

Type

Fixed Pointr

Datasheet

1.MSC7119VF1200.pdf

(60 pages)

Specifications of KMSC7119VM1200

Interface

Host Interface, I²C, UART

Clock Rate

300MHz

Non-volatile Memory

ROM (8 kB)

On-chip Ram

464kB

Voltage - I/o

3.30V

Voltage - Core

1.20V

Operating Temperature

-40°C ~ 105°C

Mounting Type

*

Package / Case

400-MAPBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KMSC7119VM1200

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

2.5.13

Freescale Semiconductor

Note:

No.

700

701

702

703

704

705

706

707

708

709

710

711

712

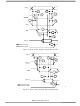

TCK frequency of operation (1/(T

Note:

TCK cycle time

TCK clock pulse width measured at V

TCK rise and fall times

Boundary scan input data set-up time

Boundary scan input data hold time

TCK low to output data valid

TCK low to output high impedance

TMS, TDI data set-up time

TMS, TDI data hold time

TCK low to TDO data valid

TCK low to TDO high impedance

TRST assert time

All timings apply to OCE module data transfers as the OCE module uses the JTAG port as an interface.

JTAG Signals

(Input)

TCK

T

frequency must less than 1/3 of the core frequency with an absolute

maximum limit of 40 MHz.

C

= 1/CLOCK which is the period of the core clock. The TCK

Characteristics

Figure 26. Test Clock Input Timing Diagram

703

C

× 3)

V

IH

M =

1.6 V

MSC7119 Data Sheet, Rev. 8

Table 31. JTAG Timing

V

IL

V

M

701

703

702

V

M

100.0

Min

25.0

11.0

14.0

14.0

0.0

0.0

5.0

0.0

0.0

5.0

0.0

0.0

All frequencies

Max

40.0

20.0

20.0

24.0

10.0

3.0

—

—

—

—

—

—

—

Unit

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

39