Chameleon-AVR Nurve Networks, Chameleon-AVR Datasheet - Page 43

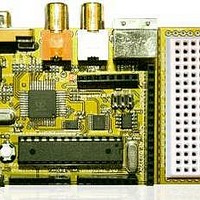

Chameleon-AVR

Manufacturer Part Number

Chameleon-AVR

Description

MCU, MPU & DSP Development Tools AVR8 & PROPELLER DEV SYSTEM (SBC)

Manufacturer

Nurve Networks

Datasheet

1.CHAMELEON-AVR.pdf

(268 pages)

Specifications of Chameleon-AVR

Processor To Be Evaluated

AVR 328P

Data Bus Width

8 bit

Interface Type

USB, VGA, PS/2, I2C, ISP, SPI

Operating Supply Voltage

3.3 V, 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 43 of 268

- Download datasheet (17Mb)

generating 480 lines of video, when complete, back to the Vsync timing region (S) the front porch for 0.35 ms and then the

frame is complete.

The thing to remember is that unlike composite video, a VGA signal needs to be driven by multiple signals for each of the

constituent controls; R, G, B, Hsync, and VSync which in my opinion is much easier than modulating and mixing them all

together as in NTSC which is a blood bath of crosstalk and noise! Now, that we have the horizontal and vertical timing for

VGA covered, let’s review the actual video data portion of the signal during the active video and see what that’s all about.

10.3.3 Generating the Active VGA Video

Generating the actual RGB video pixels is trivial on any system, there is no look up, no math, just send out bytes or words

that represent the RGB values and that’s it. Of course the Propeller will do this for us via the VSU and a driver, but there is

no reason you can’t drive the I/O pins manually with pure software as well. Either way, let’s take a look at the mechanics

of the signal. On the Chameleon AVR for example, there are 2-bits per channel, so the encoding of the VGA data byte is

as simple as generating bytes in the format shown in Figure 10.4.

Let’s say that we have a BYTE buffer called vga_byte[ ] and a function Write_VGA(value, time_us) that we use to send

data to the VGA port, given that, we can write all kinds of functions that send out different signals as long as we stream

the bytes to the port at the 25.175MHz rate everything will work out fine. For example, say that we are working with a

positive sync system, that is a VGA monitor that wants a TTL HIGH for sync, then to generate a Hsync pulse we could

use some pseudo-code like this:

Ok, now consider we want to draw 640 pixels from an array video_buffer[ ] that is storing the pixel data in byte format

already in the proper format for our hardware, then all we would do is this:

Of course, you would need some might fast hardware to delay at a resolution of 39 ns, but you get the idea. This is a

“model” of the algorithm for a line of video, this coupled with the model for the horizontal timing, vertical timing, and put it

all together as a state machine and you have a VGA generator! The VGA drivers on the Propeller are more complex than

this of course, but that’s the idea.

Table 10.4 – The RGB signals and their relationship to VGA and the Propeller I/O pins.

Prop Port Bit Chameleon Signal

P23

P22

P21

P20

P19

P18

P17

P16

VGA_RED_B1

VGA_RED_B0

VGA_GREEN_B1

VGA_GREEN_B0

VGA_BLUE_B1

VGA_BLUE_B0

VGA_HSYNC

VGA_VSYNC

Figure 10.4 – VGA data byte encoding.

e Port Mapping Bits.

© 2009 NURVE NETWORKS LLC “Exploring the Chameleon AVR 8-Bit”

Description

Bit 1 of RED channel.

Bit 0 of RED channel.

Bit 1 of GREEN channel.

Bit 0 of GREEN channel.

Bit 1 of BLUE channel.

Bit 0 of BLUE channel.

VGA HSYNC TTL level.

VGA VSYNC TTL level.

43

Related parts for Chameleon-AVR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MCU, MPU & DSP Development Tools PIC24 & PROPELLER DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools PIC24 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks