PSD813F2-A-70J STMicroelectronics, PSD813F2-A-70J Datasheet - Page 34

PSD813F2-A-70J

Manufacturer Part Number

PSD813F2-A-70J

Description

Manufacturer

STMicroelectronics

Datasheet

1.PSD813F2-A-70J.pdf

(128 pages)

Specifications of PSD813F2-A-70J

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Operating Temperature Classification

Commercial

Package Type

PLCC

Mounting

Surface Mount

Pin Count

52

Lead Free Status / RoHS Status

Compliant

- Current page: 34 of 128

- Download datasheet (2Mb)

Programming Flash memory

8

8.1

34/128

Programming Flash memory

Flash memory must be erased prior to being programmed. A byte of Flash memory is

erased to all 1s (FFh), and is programmed by setting selected bits to ’0.’ The MCU may

erase Flash memory all at once or by-sector, but not byte-by-byte. However, the MCU may

program Flash memory byte-by-byte.

The primary and secondary Flash memories require the MCU to send an instruction to

program a byte or to erase sectors (see

Once the MCU issues a Flash memory Program or Erase instruction, it must check for the

status bits for completion. The embedded algorithms that are invoked inside the PSD

support several means to provide status to the MCU. Status may be checked using any of

three methods: Data Polling, Data Toggle, or Ready/Busy (PC3).

Data Polling

Polling on the Data Polling flag bit (DQ7) is a method of checking whether a program or

erase cycle is in progress or has completed.

When the MCU issues a Program instruction, the embedded algorithm within the PSD

begins. The MCU then reads the location of the byte to be programmed in Flash memory to

check status. The Data Polling flag bit (DQ7) of this location becomes the complement of b7

of the original data byte to be programmed. The MCU continues to poll this location,

comparing the Data Polling flag bit (DQ7) and monitoring the Error flag bit (DQ5). When the

Data Polling flag bit (DQ7) matches b7 of the original data, and the Error flag bit (DQ5)

remains ’0,’ the embedded algorithm is complete. If the Error flag bit (DQ5) is '1,' the MCU

should test the Data Polling flag bit (DQ7) again since the Data Polling flag bit (DQ7) may

have changed simultaneously with the Error flag bit (DQ5, see

The Error flag bit (DQ5) is set if either an internal timeout occurred while the embedded

algorithm attempted to program the byte or if the MCU attempted to program a '1' to a bit

that was not erased (not erased is logic '0').

It is suggested (as with all Flash memories) to read the location again after the embedded

programming algorithm has completed, to compare the byte that was written to the Flash

memory with the byte that was intended to be written.

When using the Data Polling method during an Erase cycle,

the Data Polling flag bit (DQ7) is '0' until the Erase cycle is complete. A 1 on the Error flag bit

(DQ5) indicates a timeout condition on the Erase cycle; a 0 indicates no error. The MCU can

read any location within the sector being erased to get the Data Polling flag bit (DQ7) and

the Error flag bit (DQ5).

PSDsoft Express generates ANSI C code functions which implement these Data Polling

algorithms.

Doc ID 7833 Rev 7

Table

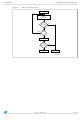

Figure 6

10).

shows the Data Polling algorithm.

Figure 6

Figure

still applies. However,

6).

PSD8XXFX

Related parts for PSD813F2-A-70J

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Flash In-System-Programmable Microcontroller Peripheral

Manufacturer:

STMicroelectronics

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: