FMS7401LEN Fairchild Semiconductor, FMS7401LEN Datasheet - Page 50

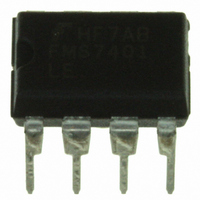

FMS7401LEN

Manufacturer Part Number

FMS7401LEN

Description

IC CTRLR POWER DGTL EEPROM 8DIP

Manufacturer

Fairchild Semiconductor

Datasheet

1.FMS7401LVN.pdf

(81 pages)

Specifications of FMS7401LEN

Applications

Digital Power Controller

Core Processor

8-Bit

Program Memory Type

EEPROM (1 kB)

Ram Size

64 x 8

Number Of I /o

6

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Through Hole

Package / Case

8-DIP (0.300", 7.62mm)

Mounting Style

Through Hole

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Interface

-

Controller Series

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

FMS7401LEN_NL

FMS7401LEN_NL

FMS7401LEN_NL

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

FMS7401LEN14

Manufacturer:

Rohm

Quantity:

21 626

PRODUCT SPECIFICATION

FMS7401L

10.2 Addressing Modes

The microcontroller core has seven instruction addressing modes: inherent, immediate, direct, indirect, indexed, absolute jump

and relative jump (see

Table

24).

Inherent

The inherent addressing mode instructions either have no operand associated or the contents of the operand are already known

to the microcontroller core. The microcontroller core then inherently knows how to execute the instruction without needing

any additional information provided by additional operands.

Immediate

2

3

The immediate addressing mode instructions contain a 3-bit,

8-bit or 12-bit

immediate field as an operand. Immediate

addressing is so-named because the value needed to complete the instruction is provided immediately to the core within the

instruction code. That is to say, the instruction itself dictates what the data value is to be e.g. stored in a register.

Direct

The direct addressing mode instructions contain an 8-bit address operand that directly points to a location within the data

memory space. Direct addressing is so-named because the value needed to complete the instruction must be directly accessed

by the core from the memory address provided by the instruction code.

Indirect

The indirect addressing mode instructions use the content in XLO, X[7:0], to address a specific location within the data mem-

4

ory space (0x00 – 0xFF).

Indirect addressing is so-named because the value needed to complete the instruction must be

retrieved indirectly by the core from the address provided by the X-pointer.

Indexed

The indexed offset addressing mode instructions add an 8-bit unsigned offset value to the X-pointer yielding a new effective

address to select a specific location anywhere within the memory map (both program and data memory space, 0x000-0xFFF).

Indexed addressing expands the functions of indirect addressing by providing the only means to access the data stored within

the program memory space.

Absolute

The absolute jump addressing mode instructions (e.g. JMP and JSR) replace the program counter with the value in the operand

5

field. This allows jumping to any location within the program memory space.

Relative

The opcode instruction field for the relative jump addressing mode instruction, JP, is calculated from the distance to the abso-

lute program memory location in the operand addressing the next instruction to be executed. The base opcode for JP is 0xC0

where bit 5 indicates the direction within memory to jump. Bits 4 to 0 indicate the number of bytes to jump where the maxi-

mum distance is 31 bytes. If bit 5 is zero, the address for the next instruction executed is determined by subtracting the lower 5

bits of the opcode (0xC1-0xDF) from the program counter; otherwise, the lower 5 bits of the opcode (0xE0-0xFF) are added to

6

the program counter.

50

REV. 1.0.3 1/24/05