MC68MH360ZP33L Freescale Semiconductor, MC68MH360ZP33L Datasheet - Page 62

MC68MH360ZP33L

Manufacturer Part Number

MC68MH360ZP33L

Description

IC MPU 32BIT QUICC 357-PBGA

Manufacturer

Freescale Semiconductor

Specifications of MC68MH360ZP33L

Processor Type

M683xx 32-Bit

Speed

33MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

357-PBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68MH360ZP33L

Manufacturer:

FREESCALE

Quantity:

1 831

Company:

Part Number:

MC68MH360ZP33L

Manufacturer:

MOTOLOLA

Quantity:

672

Company:

Part Number:

MC68MH360ZP33L

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC68MH360ZP33L

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MC68MH360ZP33LR2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 62 of 962

- Download datasheet (5Mb)

Signal Descriptions

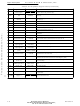

2.2 SYSTEM BUS SIGNAL INDEX IN SLAVE MODE

The CONFIG2–CONFIG0 pins are used to cause the QUICC to enter the slave mode. The

signal name, mnemonic, and a brief functional description are presented in Table 2-7. The

rest of the QUICC pins maintain their functionality in slave mode. See Section 4 Bus Oper-

ation for details.

Additionally, the QUICC provides special support for the MC68EC040 bus (or other

MC68040 family members) during slave mode. The MC68EC040 signals are marked in

boldface in the table. For more information on MC68EC040 bus operation, see M68040UM/

AD, M68040 User's Manual . The QUICC MC68EC040 support is described in Section 4 Bus

Operation and Section 6 System Integration Module (SIM60).

2-14

IPIPE0/IFETCH

RMC/CONFIG0

Master Mode

Mnemonic

CONFIG2

FC2–FC0

FREEZE/

DSACK1

DSACK0

IRQ1,4,6

BGACK

BERR

BKPT

TRIS

FC3

DS

BR

BG

Bus Grant Acknowl-

Transfer Acknowl-

Transfer Burst In-

Configuration Pin 2

Transfer Modifier

Data and Size Ac-

Data and Size Ac-

Interrupt Request/

Interrupt Outputs

Function Codes/

040 Lock Cycle/

Function Code/

Configuration 0

Transfer Type

Transfer Type

Transfer Error

Breakpoint Out

Acknowledge

Burst Address

Transfer Start

Signal Name

Bus Request

Freeze/Initial

Slave Mode

Data Strobe/

knowledge/

knowledge/

Bus Busy

Bus Error/

Bus Grant

Table 2-7. System Bus Signal Index (Slave Mode)

edge

edge

hibit

Freescale Semiconductor, Inc.

For More Information On This Product,

BADD3–BADD2 Address lines 2,3 generated by the QUICC on behalf of the

IOUT2–IOUT0/

DSACK1/TA

Slave Mode

Mnemonic

FC2–FC0/

TM2–TM0

CONFIG0

CONFIG2

DSACK0/

IRQ6,4,1/

FC3/TT0

IRQOUT

MBARE/

MC68360 USER’S MANUAL

BGACK

DS/TT1

BKPTO

BERR/

LOCK/

TEA

Go to: www.freescale.com

TBI

BR

BG

BG

BB

TS

BR

Identifies the processor state and the address space of the cur-

rent bus cycle (I/O), or indicates the MC68EC040 supplement

information about the access (I).

Identifies the DMA address space of the current bus cycle (I/O),

or indicates the MC68EC040 general transfer type: normal,

MOVE16, alternate logical function code, and acknowledge

(I).

Data strobe (I/O), or indicates the MC68EC040 general trans-

fer type: normal, MOVE16, alternate logical function code,

and acknowledge (I).

Provides asynchronous data transfers and dynamic bus sizing;

for the MC68EC040, asserted to acknowledge bus transfer.

(Both are open-drain I/O but driven high before three-stated.)

Provides asynchronous data transfers and dynamic bus sizing;

for the MC68EC040, indicates that a slave cannot handle a

line burst access. (Both are open-drain I/O but driven high be-

fore three-stated.)

BERR indicates an erroneous bus operation is being attempted

by the QUICC (open-drain I/O); TEA indicates the same for

the MC68EC040 (open-drain I/O)

Indicates the beginning of an MC68040 bus transfer. (I)

MC68EC040, for MC68EC040 burst memory cycles. (O)

Asserted by the QUICC to request bus mastership (O.D. O), or

bus request input from the MC68040. (I)

Asserted by external logic to grant bus mastership to the QUICC

(I), or bus grant output to the MC68040. (O)

Indicates that an external device or the QUICC has assumed

bus mastership. (Open-drain I/O but driven high before three-

stated).

An MC68040 LOCK signal input to prevent the QUICC from

obtaining the system bus during locked cycles (I), and the

initial QUICC configuration select (I).

Signals a hardware breakpoint to the external CPU. (O)

Provides an MBAR access enable (I), or the initial QUICC con-

figuration select. (I)

Provides an interrupt request to the QUICC interrupt controller

(I), or interrupt output signals (O) (either RQOUT as a single re-

quest or IOUT2–IOUT0 encoded).

Slave Mode Function

MOTOROLA

Related parts for MC68MH360ZP33L

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: