MC68MH360ZP33L Freescale Semiconductor, MC68MH360ZP33L Datasheet - Page 824

MC68MH360ZP33L

Manufacturer Part Number

MC68MH360ZP33L

Description

IC MPU 32BIT QUICC 357-PBGA

Manufacturer

Freescale Semiconductor

Specifications of MC68MH360ZP33L

Processor Type

M683xx 32-Bit

Speed

33MHz

Voltage

5V

Mounting Type

Surface Mount

Package / Case

357-PBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68MH360ZP33L

Manufacturer:

FREESCALE

Quantity:

1 831

Company:

Part Number:

MC68MH360ZP33L

Manufacturer:

MOTOLOLA

Quantity:

672

Company:

Part Number:

MC68MH360ZP33L

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC68MH360ZP33L

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MC68MH360ZP33LR2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 824 of 962

- Download datasheet (5Mb)

Electrical Characteristics

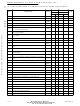

10.9BUS OPERATION AC TIMING SPECIFICATIONS (CONTINUED

10-12

Num.

NOTES:

88

89

90

91

92

1. All AC timing is shown with respect to 0.8 V and 2.0 V levels unless otherwise noted.

2. This number can be reduced to 5 ns if strobes have equal loads.

3. If multiple chip selects are used, the CS¯ width negated (#15) applies to the time from the negation of a heavily load-

4. These hold times are specified with respect to DS or CS¯ on asynchronous reads and with respect to CLKO1 on fast

5. If the asynchronous setup time (#47) requirements are satisfied, the DSACK¯ low to data setup time (#31) and

6. To ensure coherency during every operand transfer, BG will not be asserted in response to BR until after cycles of

7. In the absence of DSACK¯ , BERR is an asynchronous input using the asynchronous setup time (#47).

8. During interrupt acknowledge cycles, the processor may insert up to two wait states between states S0 and S1.

9. These specs are for Synchronous Arbitration only. ASTM=1.

10.These CS¯ specs are for TRLX=0. If RAS¯ and RAS¯DD are connected together, reduce max value of RAS¯ spec-

11.These CS¯ specs are for TRLX=1. If RAS¯ and RAS¯DD are connected together, reduce max value of RAS¯ spec-

12.These CS¯ specs are for CSNTQ=0.

13.These CS¯ specs are for CSNTQ=1; or RAS¯ specs for DRAM accesses.

14.These specs are read cycles with parity check and PBEE=1.

15.These specs are read cycles with parity check and PBEE=0,PAREN=1.

16.These RAS¯ specs are for page miss case.

17. These specifications only apply to CS¯/RAS¯ pins.

18. This specification applies to non fast termination cycles. In fast termination cycles, the BERR signal must be negated

ed chip select to the assertion of a lightly loaded chip select.

termination reads. The user is free to use either hold time for fast termination reads.

DSACK¯ low to BERR low setup time (#48) can be ignored. The data must only satisfy the data-in to CLKO1 low

setup time (#27) for the following clock cycle: BERR must only satisfy the late BERR low to CLKO1 low setup time

(#27A) for the following clock cycle.

the current operand transfer are complete and RMC is negated.

ification by 1.5ns.

ification by 1.5ns.

by 20ns after negation of AS, DS.

CLKO1 High to IFETCH High Impedance

CLKO1 High to IFETCH Valid

CLKO1 High to PERR Asserted

CLKO1 High to PERR Negated

Minimum Vcc Ramp-Up Time At Power-On Reset

Characteristic

Freescale Semiconductor, Inc.

For More Information On This Product,

MC68360 USER’S MANUAL

Go to: www.freescale.com

Symbol

t CHPA

t CHPN

t RMIN

t IFZ

t IF

3.3 V/5.0 V

Min

25.0 MHz

0

0

5

0

0

Max

35

35

20

20

-

Min

0

0

0

0

5

33.34MHz

5.0V

26.25

26.25

Max

15

15

-

MOTOROLA

Unit

ms

ns

ns

ns

ns

Related parts for MC68MH360ZP33L

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: