R8A77850BDBGV#RD0Z Renesas Electronics America, R8A77850BDBGV#RD0Z Datasheet - Page 173

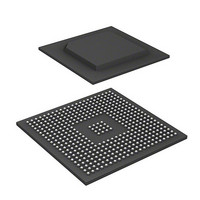

R8A77850BDBGV#RD0Z

Manufacturer Part Number

R8A77850BDBGV#RD0Z

Description

IC SUPERH MPU ROMLESS 436BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850BDBGV#RD0Z

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 173 of 1694

- Download datasheet (9Mb)

(2)

This instruction is basically used for the following purposes:

• Matrix (4 × 4) ⋅ vector (4):

• Matrix (4 × 4) × matrix (4 × 4):

Since an inexact exception is not detected by an FIRV instruction, the inexact exception (I) bit in

both the FPU exception cause field and flag field are always set to 1 when an FTRV instruction is

executed. Therefore, if the I bit is set in the FPU exception enable field, FPU exception handling

will be executed. It is not possible to check all data types in the registers beforehand when

executing an FTRV instruction. If the V bit is set in the FPU exception enable field, FPU

exception handling will be executed.

(3)

This instruction modifies banked registers. For example, when the FTRV instruction is executed,

matrix elements must be set in an array in the background bank. However, to create the actual

elements of a translation matrix, it is easier to use registers in the foreground bank. When the LDS

instruction is used on FPSCR, this instruction takes four to five cycles in order to maintain the

FPU state. With the FRCHG instruction, the FR bit in FPSCR can be changed in one cycle.

6.6.2

In addition to the powerful new geometric operation instructions, this LSI also supports high-

speed data transfer instructions.

When the SZ bit is 1, this LSI can perform data transfer by means of pair single-precision data

transfer instructions.

• FMOV DRm/XDm, DRn/XDRn (m, n: 0, 2, 4, 6, 8, 10, 12, 14)

• FMOV DRm/XDm, @Rn (m: 0, 2, 4, 6, 8, 10, 12, 14; n: 0 to 15)

These instructions enable two single-precision (2 × 32-bit) data items to be transferred; that is, the

transfer performance of these instructions is doubled.

• FSCHG

This operation is generally used for viewpoint changes, angle changes, or movements called

vector transformations (4-dimensional). Since affine transformation processing for angle +

parallel movement basically requires a 4 × 4 matrix, this LSI supports 4-dimensional

operations.

This operation requires the execution of four FTRV instructions.

FTRV XMTRX, FVn (n: 0, 4, 8, 12)

FRCHG

Pair Single-Precision Data Transfer

Rev.1.00 Jan. 10, 2008 Page 141 of 1658

6. Floating-Point Unit (FPU)

REJ09B0261-0100

Related parts for R8A77850BDBGV#RD0Z

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: