R8A77850BDBGV#RD0Z Renesas Electronics America, R8A77850BDBGV#RD0Z Datasheet - Page 241

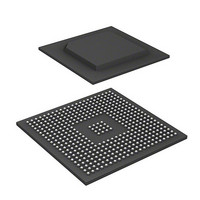

R8A77850BDBGV#RD0Z

Manufacturer Part Number

R8A77850BDBGV#RD0Z

Description

IC SUPERH MPU ROMLESS 436BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850BDBGV#RD0Z

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 241 of 1694

- Download datasheet (9Mb)

7.10

7.10.1

When using an LDTLB instruction instead of software to a value to the MMUCR. URC, execute 1

or 2 below.

1. In 29-bit address mode, follow A. and B. below. In 32-bit address mode, follow A. through D.

2. If a TLB miss exception occurs, add 1 to MMUCR.URC before executing an LDTLB

below.

A. Place the TLB miss exception handling routine*

B. Use only one page of the PMB for instruction accesses*

C. In 32-bit address mode, obey 1 and 2 below when recording information in the UTLB in

D. Do not make an attempt to execute the FDIV or FSQRT instruction in the TLB miss

instruction.

memory so that all the instruction accesses*

should occur solely in the P1, P2 area, or the on-chip memory. Clear the RP bit in the

RAMCR register to 0 (initial value), when the TLB miss exception handling routine is

placed in the on-chip memory.

handling routine*

of the PMB.

the MMU-related exception*

a. When thea TLB miss exception occurs, and recording the information of a page with

b. When an initial page write exception occurs and the TLB entry in the UTLB of which

exception handling routine.

Usage Notes

Note on Using LDTLB Instruction

the access right in the UTLB, do not record the page, in which the exception has

occurred, in the UTLB using the following two operations.

the dirty bit is 1 is replaced, before the write instruction for the page corresponding to

this replaced TLB entry is completed, register the TLB entry of which the dirty bit is 1.

⎯ Specifies the protection key data that causes a protection violation exception upon

⎯ Specifies the protection key data that does not cause a protection violation

re-execution of the instruction that has caused the TLB miss exception and records

the page, in which the TLB miss exception has occurred, in the UTLB.

exception in the protection violation exception handling routine to record the page

in the UTLB and re-executes the instruction that has caused the protection violation

exception.

1

. In 32-bit address mode, do not place them in the last 64 bytes of a page

2

handling routine.

3

in the TLB miss exception handling routine

1

only in the P1, P2 area ,or the on-chip

Rev.1.00 Jan. 10, 2008 Page 209 of 1658

3

in the TLB miss exception

7. Memory Management Unit (MMU)

REJ09B0261-0100

Related parts for R8A77850BDBGV#RD0Z

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: