LFXP2-30E-5FN484C LATTICE SEMICONDUCTOR, LFXP2-30E-5FN484C Datasheet - Page 15

LFXP2-30E-5FN484C

Manufacturer Part Number

LFXP2-30E-5FN484C

Description

IC, LATTICEXP2 FPGA, 435MHZ, FPBGA-484

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeXP2r

Datasheet

1.LFXP2-5E-5TN144C.pdf

(93 pages)

Specifications of LFXP2-30E-5FN484C

No. Of Logic Blocks

29000

No. Of Macrocells

14500

Family Type

LatticeXP2

No. Of Speed Grades

5

No. Of I/o's

363

Clock Management

PLL

Total Ram Bits

387Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFXP2-30E-5FN484C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Lattice Semiconductor

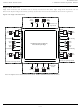

Primary Clock Routing

The clock routing structure in LatticeXP2 devices consists of a network of eight primary clock lines (CLK0 through

CLK7) per quadrant. The primary clocks of each quadrant are generated from muxes located in the center of the

device. All the clock sources are connected to these muxes. Figure 2-9 shows the clock routing for one quadrant.

Each quadrant mux is identical. If desired, any clock can be routed globally.

Figure 2-9. Per Quadrant Primary Clock Selection

Dynamic Clock Select (DCS)

The DCS is a smart multiplexer function available in the primary clock routing. It switches between two independent

input clock sources without any glitches or runt pulses. This is achieved irrespective of when the select signal is

toggled. There are two DCS blocks per quadrant; in total, eight DCS blocks per device. The inputs to the DCS block

come from the center muxes. The output of the DCS is connected to primary clocks CLK6 and CLK7 (see Figure 2-

9).

Figure 2-10 shows the timing waveforms of the default DCS operating mode. The DCS block can be programmed

to other modes. For more information on the DCS, please see TN1126, LatticeXP2 sysCLOCK PLL Design and

Usage Guide .

Figure 2-10. DCS Waveforms

Secondary Clock/Control Routing

Secondary clocks in the LatticeXP2 devices are region-based resources. EBR rows, DSP rows and a special verti-

cal routing channel bound the secondary clock regions. This special vertical routing channel aligns with either the

left edge of the center DSP block in the DSP row or the center of the DSP row. Figure 2-11 shows this special ver-

tical routing channel and the eight secondary clock regions for the LatticeXP2-40. LatticeXP2-30 and smaller

CLK0

30:1

SEL

CLK1

CLK0

DCSOUT

CLK1

30:1

CLK2

Primary Clock Feedlines: PLLs + CLKDIVs + PIOs + Routing

30:1

8 Primary Clocks (CLK0 to CLK7) per Quadrant

CLK3

30:1

CLK4

30:1

2-12

CLK5

30:1

29:1

CLK6

DCS

LatticeXP2 Family Data Sheet

29:1

29:1

CLK7

DCS

29:1

Architecture