LFXP2-30E-5FN484C LATTICE SEMICONDUCTOR, LFXP2-30E-5FN484C Datasheet - Page 72

LFXP2-30E-5FN484C

Manufacturer Part Number

LFXP2-30E-5FN484C

Description

IC, LATTICEXP2 FPGA, 435MHZ, FPBGA-484

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeXP2r

Datasheet

1.LFXP2-5E-5TN144C.pdf

(93 pages)

Specifications of LFXP2-30E-5FN484C

No. Of Logic Blocks

29000

No. Of Macrocells

14500

Family Type

LatticeXP2

No. Of Speed Grades

5

No. Of I/o's

363

Clock Management

PLL

Total Ram Bits

387Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFXP2-30E-5FN484C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Lattice Semiconductor

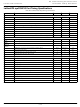

LatticeXP2 sysCONFIG Port Timing Specifications

sysCONFIG POR, Initialization and Wake Up

t

t

t

t

t

t

t

t

t

t

sysCONFIG SPI Port (Master)

t

t

t

t

t

f

t

t

sysCONFIG SPI Port (Slave)

f

t

t

t

t

t

t

t

t

t

t

t

ICFG

VMC

PRGMRJ

PRGM

DINIT

DPPINIT

DPPDONE

IODISS

IOENSS

MWC

CFGX

CSSPI

CSCCLK

SOCDO

CSPID

MAXSPI

SUSPI

HSPI

MAXSPIS

RF

STCO

STOZ

STSU

STH

STCKH

STCKL

STVO

SCS

SCSS

SCSH

Parameter

Minimum Vcc to INITN High

Time from tICFG to valid Master CCLK

PROGRAMN Pin Pulse Rejection

PROGRAMN Low Time to Start Configuration

PROGRAMN High to INITN High Delay

Delay Time from PROGRAMN Low to INITN Low

Delay Time from PROGRAMN Low to DONE Low

User I/O Disable from PROGRAMN Low

User I/O Enabled Time from CCLK Edge During Wake-up Sequence

Additional Wake Master Clock Signals after DONE Pin High

INITN High to CCLK Low

INITN High to CSSPIN Low

CCLK Low before CSSPIN Low

CCLK Low to Output Valid

CSSPIN[0:1] Low to First CCLK Edge Setup Time

Max CCLK Frequency

SOSPI Data Setup Time Before CCLK

SOSPI Data Hold Time After CCLK

Slave CCLK Frequency

Rise and Fall Time

Falling Edge of CCLK to SOSPI Active

Falling Edge of CCLK to SOSPI Disable

Data Setup Time (SISPI)

Data Hold Time (SISPI)

CCLK Clock Pulse Width, High

CCLK Clock Pulse Width, Low

Falling Edge of CCLK to Valid SOSPI Output

CSSPISN High Time

CSSPISN Setup Time

CSSPISN Hold Time

Over Recommended Operating Conditions

Description

3-28

DC and Switching Characteristics

LatticeXP2 Family Data Sheet

2cyc

0.02

0.02

Min

50

10

50

10

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

25

25

25

0

0

7

8

600+6cyc

Max

200

200

50

12

—

50

50

35

25

—

—

15

20

—

—

25

20

20

20

—

—

—

—

—

—

2

1

1

2

mV/ns

cycles

Units

MHz

MHz

ms

ms

µs

ns

ns

ns

ns

ns

ns

µs

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

µs

ns

ns

ns

ns