ADSP-TS101SAB2-000 Analog Devices Inc, ADSP-TS101SAB2-000 Datasheet - Page 14

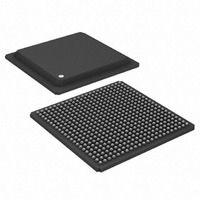

ADSP-TS101SAB2-000

Manufacturer Part Number

ADSP-TS101SAB2-000

Description

IC,DSP,32-BIT,BGA,484PIN,PLASTIC

Manufacturer

Analog Devices Inc

Series

TigerSHARC®r

Type

Fixed/Floating Pointr

Datasheet

1.ADSP-TS101SAB1-000.pdf

(48 pages)

Specifications of ADSP-TS101SAB2-000

Rohs Status

RoHS non-compliant

Interface

Host Interface, Link Port, Multi-Processor

Clock Rate

250MHz

Non-volatile Memory

External

On-chip Ram

768kB

Voltage - I/o

3.30V

Voltage - Core

1.20V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

484-BGA

Package

484BGA

Numeric And Arithmetic Format

Fixed-Point|Floating-Point

Maximum Speed

250 MHz

Ram Size

768 KB

Device Million Instructions Per Second

250 MIPS

Lead Free Status / RoHS Status

Other names

ADSP-TS101SAB2000

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADSP-TS101SAB2-000

Manufacturer:

MINI

Quantity:

1 400

Company:

Part Number:

ADSP-TS101SAB2-000

Manufacturer:

Analog Devices Inc

Quantity:

10 000

ADSP-TS101S

Table 5. Pin Definitions—External Port Bus Controls (Continued)

1

2

3

4

Table 6. Pin Definitions—External Port Arbitration

Signal

MSH

BRST

Type column symbols: A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply;

pd = internal pull-down approximately 100 k

Term (for termination) column symbols: epd = external pull-down approximately 10 k

to V

Signal

BR7–0

ID2–0

BM

BOFF

BUSLOCK

HBR

Type column symbols: A = asynchronous; G = ground; I = input; O = output; o/d = open drain output; P = power supply;

pd = internal pull-down approximately 100 k

Term (for termination) column symbols: epd = external pull-down approximately 10 k

to V

The address and data buses may float for several cycles during bus mastership transitions between a TigerSHARC processor and a host. Floating in this case means that these

The internal pull-up may not be sufficient. A stronger pull-up may be necessary.

See

The internal pull-down may not be sufficient. A stronger pull-down may be necessary.

inputs are not driven by any source and that dc-biased terminations are not present. It is not necessary to add pull-ups as there are no reliability issues and the worst-case

power consumption for these floating inputs is negligible. Unconnected address pins may require pull-ups or pull-downs to avoid erroneous slave accesses, depending on

the system. Unconnected data pins may be left floating.

Electrical Characteristics on Page 20

1

DD-IO

DD-IO

2

2

1

, nc = not connected; au = always used.

, nc = not connected; au = always used.

3

Type

O/T (pu

I/O/T (pu

Type

I/O

I (pd

O (pd

I

O/T (pu

I

2

)

2

)

3

2

)

)

3

)

for maximum and minimum current consumption for pull-up and pull-down resistances.

Term

nc

nc

Term

epu

au

au

epu

nc

epu

Description

Memory Select Host. MSH is asserted whenever the DSP accesses the host address space

(ADDR31:28 0b0000). MSH is a decoded memory address pin that changes concurrently with

ADDR pins. In a multiprocessor system, the bus master DSP drives MSH.

Burst. The current bus master (DSP or host) asserts this pin to indicate that it is reading or writing

data associated with consecutive addresses. A slave device can ignore addresses after the first

one and increment an internal address counter after each transfer. For host-to-DSP burst

accesses, the DSP increments the address automatically while BRST is asserted.

Description

Multiprocessing Bus Request Pins. Used by the DSPs in a multiprocessor system to arbitrate for

bus mastership. Each DSP drives its own BRx line (corresponding to the value of its ID2–0 inputs)

and monitors all others. In systems with fewer than eight DSPs, set the unused BRx pins high.

Multiprocessor ID. Indicates the DSP’s ID. From the ID, the DSP determines its order in a multi-

processor system. These pins also indicate to the DSP which bus request (BR0–BR7) to assert

when requesting the bus: 000 = BR0, 001 = BR1, 010 = BR2, 011 = BR3, 100 = BR4, 101 = BR5,

110 = BR6, or 111 = BR7. ID2–0 must have a constant value during system operation and can

change during reset only.

Bus Master. The current bus master DSP asserts BM. For debugging only. At reset this is a strap

pin. For more information, see

Back Off. A deadlock situation can occur when the host and a DSP try to read from each other’s

bus at the same time. When deadlock occurs, the host can assert BOFF to force the DSP to

relinquish the bus before completing its outstanding transaction, but only if the outstanding

transaction is to host memory space (MSH).

Bus Lock Indication. Provides an indication that the current bus master has locked the bus.

Host Bus Request. A host must assert HBR to request control of the DSP’s external bus. When

HBR is asserted in a multiprocessing system, the bus master relinquishes the bus and asserts

HBG once the outstanding transaction is finished.

; pu = internal pull-up approximately 100 k

; pu = internal pull-up approximately 100 k

Rev. C | Page 14 of 48 | May 2009

Table 16 on Page

to V

to V

; T = three-state

; T = three-state

SS

SS

19.

; epu = external pull-up approximately 10 k

; epu = external pull-up approximately 10 k