DSPD56367PV150 Freescale Semiconductor, DSPD56367PV150 Datasheet - Page 55

DSPD56367PV150

Manufacturer Part Number

DSPD56367PV150

Description

Manufacturer

Freescale Semiconductor

Datasheet

1.DSPD56367PV150.pdf

(100 pages)

Specifications of DSPD56367PV150

Device Core Size

24b

Format

Fixed Point

Clock Freq (max)

150MHz

Mips

150

Device Input Clock Speed

150MHz

Ram Size

69KB

Program Memory Size

120KB

Operating Supply Voltage (typ)

1.8/3.3V

Operating Supply Voltage (min)

1.71/3.14V

Operating Supply Voltage (max)

1.89/3.46V

Operating Temp Range

-40C to 95C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

144

Package Type

LQFP

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DSPD56367PV150

Manufacturer:

MOT

Quantity:

60

Company:

Part Number:

DSPD56367PV150K41R

Manufacturer:

DSP

Quantity:

59

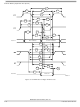

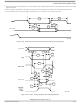

3.11

Freescale Semiconductor

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

No.

Read data strobe assertion width

HACK read assertion width

Read data strobe deassertion width

HACK read deassertion width

Read data strobe deassertion width

between two consecutive CVR, ICR, or ISR reads

HACK deassertion width after “Last Data Register” reads

Write data strobe assertion width

HACK write assertion width

Write data strobe deassertion width

HACK write deassertion width

HAS assertion width

HAS deassertion to data strobe assertion

Host data input setup time before write data strobe deassertion

Host data input setup time before HACK write deassertion

Host data input hold time after write data strobe deassertion

Host data input hold time after HACK write deassertion

Read data strobe assertion to output data active from high impedance

HACK read assertion to output data active from high impedance

Read data strobe assertion to output data valid

HACK read assertion to output data valid

Read data strobe deassertion to output data high impedance

HACK read deassertion to output data high impedance

Output data hold time after read data strobe deassertion

Output data hold time after HACK read deassertion

HCS assertion to read data strobe deassertion

HCS assertion to write data strobe deassertion

• after ICR, CVR and “Last Data Register” writes

• after IVR writes, or

• after TXH:TXM writes (with HBE=0), or

• after TXL:TXM writes (with HBE=1)

Parallel Host Interface (HDI08) Timing

Table 3-15 Host Interface (HDI08) Timing

Characteristics

8

4

4

8

4

after “Last Data Register” reads

DSP56367 Technical Data, Rev. 2.1

9

4

4

8

5

7

4

5, 6

8

4

8

5

,

6

4

, or

2.5 × T

2.5 × T

Expression

1, 2, 3

Parallel Host Interface (HDI08) Timing

T

T

C

C

—

—

—

—

—

—

—

—

—

—

—

+ 9.9

+9.9

C

C

+ 6.6

+ 6.6

16.7

23.3

13.2

23.3

16.5

16.7

Min

9.9

9.9

0.0

9.9

3.3

3.3

3.3

9.9

—

—

150 MHz

Max

24.2

9.9

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

3-31