R8A77850ADBGV#RD0Z Renesas Electronics America, R8A77850ADBGV#RD0Z Datasheet - Page 986

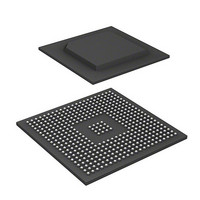

R8A77850ADBGV#RD0Z

Manufacturer Part Number

R8A77850ADBGV#RD0Z

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ADBGV#RD0Z

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

R8A77850ADBGV#RD0ZR8A77850ADBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 986 of 1694

- Download datasheet (9Mb)

19. Display Unit (DU)

19.4.16 Sync Mode

In order to facilitate synchronization with external equipment, in addition to master mode, a TV

synchronization function is provided. Selection of master mode and TV sync mode is performed

using the TVM bit in DSYSR. Regardless of the synchronization method, the position of the

falling edge of the vertical sync signal (VSYNC) set by VSPR is detected and is reflected in the

FRM bit and VBK bit in DSSR.

Master Mode (Internal Sync Mode): By setting the period and pulse width of the horizontal and

vertical sync signals (HSYNC, VSYNC) in the display timing generation register, the

corresponding waveforms are output. Also, display data is output in sync with these signals.

When in interlaced sync mode and interlaced sync & video mode, a signal is output to the ODDF

pin indicating odd/even fields.

TV Sync Mode (External Sync Mode): In TV sync mode, display data is output in sync with a

horizontal sync signal and vertical sync signal (EXHSYNC, EXVSYNC) input from a TV, video,

or other external sync signal generation circuit. Display data is output with reference to the falling

edge of the EXHSYNC signal and the rising edge of the EXVSYNC signal.

The horizontal sync signal, vertical sync signal, and clock signal from the external sync signal

generation circuit are input to the HSYNC, VSYNC, and DCLKIN pin, respectively. CSYNC is at

high level. When in interlaced sync mode and interlaced sync & video mode, a signal should be

input to the ODDF pin indicating odd/even fields. When in non-interlaced mode, the input to the

ODDF pin should be fixed at low level or at high level.

When operating the unit in TV sync mode also, values must be set in HCR, HSWR, VCR, and

VSPR (display timing generation registers).

When the EXVSYNC signal is input, either before or after completion of display of the display

size portion set in the display unit (DU), the display unit (DU) performs vertical display

completion operation and transitions to control for the next screen. When the EXVSYNC signal is

not input, the unit continues to wait for the EXVSYNC signal while remaining in the vertical

blanking interval (auto-control is not performed). Similarly, when the EXHSYNC signal is input

the display unit (DU) performs horizontal display completion operation and transitions to control

for the next raster line; but if the EXHSYNC signal is not input, the unit continues to wait for the

EXHSYNC signal while remaining in the horizontal blanking interval (auto-control is not

performed).

Rev.1.00 Jan. 10, 2008 Page 954 of 1658

REJ09B0261-0100

Related parts for R8A77850ADBGV#RD0Z

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: