ADSP-21160NCB-100 Analog Devices Inc, ADSP-21160NCB-100 Datasheet - Page 17

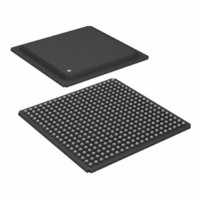

ADSP-21160NCB-100

Manufacturer Part Number

ADSP-21160NCB-100

Description

IC,DSP,32-BIT,CMOS,BGA,400PIN,PLASTIC

Manufacturer

Analog Devices Inc

Series

SHARC®r

Type

Floating Pointr

Specifications of ADSP-21160NCB-100

Rohs Status

RoHS non-compliant

Interface

Host Interface, Link Port, Serial Port

Clock Rate

100MHz

Non-volatile Memory

External

On-chip Ram

512kB

Voltage - I/o

3.30V

Voltage - Core

1.90V

Operating Temperature

-40°C ~ 100°C

Mounting Type

Surface Mount

Package / Case

400-BGA

Package

400BGA

Numeric And Arithmetic Format

Floating-Point

Maximum Speed

100 MHz

Ram Size

512 KB

Device Million Instructions Per Second

100 MIPS

Lead Free Status / RoHS Status

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADSP-21160NCB-100

Manufacturer:

Analog Devices Inc

Quantity:

10 000

Table 4. Power-up Sequencing

1

2

3

4

REV. 0

Parameter

Timing Requirements

t

t

t

t

t

Switching Characteristics

t

Valid V

Assumes a stable CLKIN signal after meeting worst-case start-up timing of oscillators. Refer to your oscillator manufacturer’s data sheet for start-up time.

Based on CLKIN cycles.

CORERST is an internal signal only. The 4096 cycle count is dependent on t

RSTVDD

IVDDEVDD

CLKVDD

CLKRST

PLLRST

CORERST

of milliseconds, depending on the design of the power supply subsystem.

be added to the core reset time, resulting in 4097 cycles maximum.

DDINT

/V

DDEXT

RESET Low Before V

V

CLKIN Running After valid V

CLKIN Valid Before RESET Deasserted

PLL Control Setup Before RESET Deasserted

DSP Core Reset Deasserted After RESET Deasserted

DDINT

RESET

V

V

CLKIN

CLK_CFG3-0

CORERST

assumes that the supplies are fully ramped to their 1.9 V and 3.3 V rails. Voltage ramp rates can vary from microseconds to hundreds

DDINT

DDEXT

on Before V

DDEXT

t

RSTVDD

VOLTAGE REGULATOR

VOLTAGE REGULATOR

DDINT

1.9V CORE

Figure 7. Dual Voltage Schottky Diode

3.3V I/O

/V

Figure 6. Power-up Sequencing

DDEXT

DDINT

t

IVDDEVDD

t

CLKVDD

on

/V

DDEXT

–17–

1

SRST

t

PLLRST

specification. If setup time is not met, one additional CLKIN cycle may

t

CLKRST

V

V

DDINT

DDEXT

t

CORERST

ADSP-21160

Min

0

– 50

0

10

20

4096t

2

3

CK

ADSP-21160N

3, 4

Max

+200

200

Unit

ns

ms

ms

µs

µs

ms