MD2433-D8G-V3Q18-X-P SanDisk, MD2433-D8G-V3Q18-X-P Datasheet - Page 47

MD2433-D8G-V3Q18-X-P

Manufacturer Part Number

MD2433-D8G-V3Q18-X-P

Description

IC MDOC H1 8GB 115-FBGA

Manufacturer

SanDisk

Datasheet

1.MD2433-D4G-V3Q18-X-P.pdf

(64 pages)

Specifications of MD2433-D8G-V3Q18-X-P

Format - Memory

FLASH

Memory Type

FLASH - Nand

Memory Size

8G (1G x 8)

Speed

64ns

Interface

Parallel

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-30°C ~ 85°C

Package / Case

115-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MD2433-D8G-V3Q18-X-P

Manufacturer:

SANDISK

Quantity:

18 120

Company:

Part Number:

MD2433-D8G-V3Q18-X-P

Manufacturer:

M-SYSTEM

Quantity:

363

Company:

Part Number:

MD2433-D8G-V3Q18-X-P

Manufacturer:

SanDisk

Quantity:

10 000

mDOC H1 4Gb (512MByte) and 8Gb (1GByte)

8-Bit (Byte) Data Access Mode

When configured for 8-bit operation, ball IF_CFG should be connected to VSS, data lines D[15:8]

are internally pulled up and may be left unconnected. The device routes odd and even address

accesses to the appropriate byte lane of the flash and RAM.

Host address SA0 must be connected to mDOC H1 A0, SA1 must be connected to A1, etc.

16-Bit (Word) Data Access Mode

To set mDOC H1 to work in 16-bit mode, the IF_CFG ball must be connected to VCCQ.

In 16-bit mode, the Programmable Boot Block is accessed as a true 16-bit device. It responds with

the appropriate data when the CPU issues either an 8-bit or 16-bit read cycle. The flash area is

accessed as a 16-bit device, regardless of the interface bus width. This has no affect on the design of

the interface between mDOC H1 and the host. The TrueFFS driver handles all issues regarding

moving data in and out of mDOC H1.

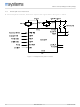

32-Bit (Double Word) Data Access Mode

In a 32-bit bus system that cannot execute byte- or word-aligned accesses, the system address lines

SA0 and SA1 are always 0. Consecutive double words (32-bit words) are differentiated by SA2

toggling. Therefore, in 32-bit systems that support only 32-bit data access cycles, mDOC H1 signal

A0 is connected to VSS and A1 is connected to the first system address bit that toggles; i.e., SA2.

System

Host

SA13

SA12

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

mDOC H1

Note:

The prefix “S” indicates system host address lines

Figure 14: Address Shift Configuration for 32-Bit Data Access Mode

47

Data Sheet, Rev. 1.1

95-DT-1104-01