TXC-03453BROG Transwitch Corporation, TXC-03453BROG Datasheet - Page 67

TXC-03453BROG

Manufacturer Part Number

TXC-03453BROG

Description

Manufacturer

Transwitch Corporation

Datasheet

1.TXC-03453BROG.pdf

(96 pages)

Specifications of TXC-03453BROG

Screening Level

Industrial

Package Type

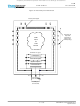

BGA

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TXC-03453BROGA

Manufacturer:

TRANSWITCH

Quantity:

5

MEMORY MAP BIT DESCRIPTIONS

Please note that all bits in used registers that are shown as Reserved or Not Used should be set to zero when

the register is written, unless otherwise indicated. If the register has not been written, or cannot be written, then

the values read from such bits may be arbitrary.

COMMON CONTROL BIT DESCRIPTIONS

Address

0C0

0C1

0C2

0C3

0C4

Bit

7-0

7-0

7-4

7-0

7-0

Proprietary TranSwitch Corporation Information for use Solely by its Customers

3

2

1

0

Symbol

ADDEN

INTZN

INTEN

L3EN

Reserved

Reserved

Reserved: Must be set to zero when register is written.

Device Interrupt High Impedance (High-Z) Off State Disable: This bit

works in conjunction with bit INTEN (bit 2) to control the operation of the

interrupt output lead INT/IRQ (lead AB8), as described in the table below. A

1 sets the INT/IRQ lead for normal operation if bit INTEN is 1. The lead will

be either high when active with the off state low (Intel mode, INT), or low

when active with the off state high (Motorola mode, IRQ). A 0 enables the

off state to be high impedance instead, for both modes.

INTZN

Device Interrupt Enable: This bit works in conjunction with bit INTZN (bit

3) as described in the table above.

Device Add Bus Enable: A 1 enables the following Add bus output signals

for a channel if the per channel control bit ADBEN is also a 1:

A 0 forces these leads to a high impedance state, or to the off state,

regardless of the state of ADBEN. A hardware or software reset forces this

bit to the 0 state.

Device Receive Output and Monitor Signals Enable: A 1 enables the

following receive output and monitor signals for a channel if the per channel

control bit L3OEN is also a 1:

A 0 forces these signals to a high impedance state, regardless of the state

of L3OEN. A hardware or software reset forces this bit to the 0 state.

Reserved

Reserved

X

0

1

- AD(7-0) data leads

- ADD add indication lead

- APAR parity lead.

- RCLKn (Receive Clock)

- RPOSn (Receive Positive Rail/NRZ)

- RNEGn (Receive Negative Rail)

- RnNRD (Transmit Monitor NRZ Data)

- RnNRC (Transmit Monitor NRZ Clock)

DATA SHEET

INTEN

- 67 of 96 -

0

1

1

Interrupt Lead Action

Held in the high impedance state

Interrupt lead enabled. Held to the high

impedance state in the off state, when no

interrupts have occurred.

Normal operation. Driven to high or low in both

active and off states, as defined in the lead

description.

Description

PRELIMINARY TXC-03453B-MB, Ed. 3

TXC-03453B

September 2003

TL3M