LCMXO2-2000HC-4FTG256C Lattice, LCMXO2-2000HC-4FTG256C Datasheet - Page 75

LCMXO2-2000HC-4FTG256C

Manufacturer Part Number

LCMXO2-2000HC-4FTG256C

Description

FPGA - Field Programmable Gate Array 2112 LUTs 207 IO 3.3V 4 Spd

Manufacturer

Lattice

Datasheet

1.LCMXO2-256HC-4SG32I.pdf

(106 pages)

Specifications of LCMXO2-2000HC-4FTG256C

Rohs

yes

Number Of Gates

2 K

Embedded Block Ram - Ebr

74 Kbit

Number Of I/os

207

Maximum Operating Frequency

269 MHz

Operating Supply Voltage

1.14 V to 3.465 V, 2.375 V to 3.465 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Package / Case

ftBGA-256

Distributed Ram

16 Kbit

Minimum Operating Temperature

0 C

Operating Supply Current

4.8 mA

Factory Pack Quantity

90

User Flash Memory - Ufm

80 Kbit

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LCMXO2-2000HC-4FTG256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Part Number:

LCMXO2-2000HC-4FTG256C

Manufacturer:

LATTICE

Quantity:

20 000

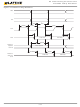

sysCONFIG Port Timing Specifications

I

SPI Port Timing Specifications

2

C Port Timing Specifications

f

1. MachXO2 supports the following modes:

2. Refer to the I

f

1. Applies to user mode only. For configuration mode timing specifications, refer to sysCONFIG Port Timing Specifications

MAX

MAX

• Standard-mode (Sm), with a bit rate up to 100 kbit/s (user and configuration mode)

• Fast-mode (Fm), with a bit rate up to 400 kbit/s (user and configuration mode)

table in this data sheet.

All Configuration Modes

t

t

t

t

t

t

Slave SPI

f

t

t

t

t

t

t

t

t

t

t

Master SPI

f

t

t

t

t

t

t

PRGM

PRGMJ

INITL

DPPINIT

DPPDONE

IODISS

MAX

CCLKH

CCLKL

STSU

STH

STCO

STOZ

STOV

SCS

SCSS

SCSH

MAX

MCLKH

MCLKL

STSU

STH

CSSPI

MCLK

Symbol

Symbol

2

Symbol

C specification for timing requirements.

Maximum SCL clock frequency

Maximum SCK clock frequency

PROGRAMN low pulse accept

PROGRAMN low pulse rejection

INITN low time

PROGRAMN low to INITN low

PROGRAMN low to DONE low

PROGRAMN low to I/O disable

CCLK clock frequency

CCLK clock pulse width high

CCLK clock pulse width low

CCLK setup time

CCLK hold time

CCLK falling edge to valid output

CCLK falling edge to valid disable

CCLK falling edge to valid enable

Chip select high time

Chip select setup time

Chip select hold time

MCLK clock frequency

MCLK clock pulse width high

MCLK clock pulse width low

MCLK setup time

MCLK hold time

INITN high to chip select low

INITN high to first MCLK edge

1, 2

1

Parameter

Parameter

Parameter

3-36

DC and Switching Characteristics

Min.

3.75

3.75

0.75

100

7.5

7.5

55

25

—

—

—

—

—

—

—

—

—

—

2

0

3

3

5

1

MachXO2 Family Data Sheet

Min.

Min.

—

—

Max.

120

133

200

25

70

80

—

55

66

—

10

10

10

—

—

—

—

—

—

—

—

—

—

1

Max.

Max.

400

45

Units

MHz

MHz

ns

ns

us

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

us

Units

Units

MHz

KHz