LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 41

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 41 of 385

- Download datasheet (3Mb)

Lattice Semiconductor

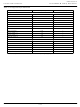

Figure 2-36. DQS Local Bus

Polarity Control Logic

In a typical DDR Memory interface design, the phase relationship between the incoming delayed DQS strobe and

the internal system clock (during the READ cycle) is unknown.

The LatticeECP2/M family contains dedicated circuits to transfer data between these domains. To prevent set-up

and hold violations, at the domain transfer between DQS (delayed) and the system clock, a clock polarity selector

is used. This changes the edge on which the data is registered in the synchronizing registers in the input register

block. This requires evaluation at the start of each READ cycle for the correct clock polarity.

Prior to the READ operation in DDR memories, DQS is in tristate (pulled by termination). The DDR memory device

drives DQS low at the start of the preamble state. A dedicated circuit detects the first DQS rising edge after the pre-

amble state. This signal is used to control the polarity of the clock to the synchronizing registers.

*DQSXFERDEL shifts ECLK1 by 90% and is not associated with a particular PIO.

DQSXFER

DQS

DQS

DCNTL[6:0]

ECLK1

DQSXFER

DCNTL[6:0]

CLK1

GSR

DQS

CEI

2-38

DQSXFERDEL*

Polarity Control

DQSDEL

Logic

PIO

PIO

To DDR

Register Block

Register Block

Reg.

Output

Input

Calibration bus

To Sync

LatticeECP2/M Family Data Sheet

from DLL

Reg.

Buffer

Buffer

sysIO

sysIO

DI

DI

Strobe

Datain

DDR

DQS

PAD

PAD

Architecture

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: