LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 90

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 90 of 385

- Download datasheet (3Mb)

Lattice Semiconductor

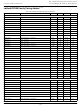

Table 3-9. SERDES/PCS Latency Breakdown (Parallel Clock Cycle)

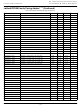

Figure 3-12. Transmitter and Receiver Block Diagram

HDOUTPi

HDOUTNi

HDINPi

HDINNi

Transmit Data Latency

Receive Data Latency

1. PCS internal Parallel Clock. This clock rate is same as the rxfullclk in table 8-6.

2. FPGA Bridge latency varies by UP/DOWN Sample FIFO read/write. These numbers were presented for

3. The maximum latency applies to bit0.

Transmitter

Receiver

REFCLK

8bit/10bit interface. The depth of Down Sample/Up Sample FIFO is 4. The earliest read can be done after

write clock cycle (1 clock) in Down Sample FIFO. The latest read will be done after the FIFO is full (4 + 1

= 5). For 16b/20b interface, the numbers become doubled. Min = 2, Max = 10. This latency depends on

the internal FIFO flag operation.

Bit1 latency = Bit0 latency + 1 UI.

Bit2 latency = Bit0 latency + 2 UI.

Item

R1

R2

R3

R4

R5

R6

T1

T2

T3

T4

EQ

TX PLL

SERDES

FPGA Bridge Transmit

8b10b Encoder

SERDES Bridge Transmit

Serializer

Deserializer

SERDES Bridge Receive

Word Alignment

8b10b Decoder

Clock Tolerance Compensation

FPGA Bridge Receive

REFCLK

CDR

Serializer

8:1/10:1

Transmit Clock

T4

Deserializer

R1

1:8/1:10

3

Description

3

SERDES Bridge

R2

BYPASS

Polarity

Adjust

2

2

BYPASS

Polarity

Adjust

T3

Recovered Clock

3-39

BYPASS

Min.

R3

WA

1

2

2

2

4

1

7

1

Encoder

BYPASS

BYPASS

DEC

PCS

Average

T2

DC and Switching Characteristics

LatticeECP2/M Family Data Sheet

R4

15

3

2

2

2

4

1

3

BYPASS

Elastic

Buffer

FIFO

R5

Max.

2.4

1.2

23

5

2

2

2

4

1

5

FPGA Bridge

Sample

Down

FIFO

Sample

R6

FIFO

Up

BYPASS

Bypass

T1

1

1

1

1

0

1

1

1

FPGA Core

FPGA

EBRD Clock

Receive Data

FPGA

Receive Clock

Transmit Data

FPGA

Transmit Clock

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: