LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 91

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 91 of 385

- Download datasheet (3Mb)

Lattice Semiconductor

SERDES High Speed Data Receiver (LatticeECP2M Family Only)

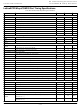

Table 3-10. Serial Input Data Specifications

Input Data Jitter Tolerance

A receiver’s ability to tolerate incoming signal jitter is very dependent on jitter type. High speed serial interface stan-

dards have recognized the dependency on jitter type and have recently modified specifications to indicate toler-

ance levels for different jitter types as they relate to specific protocols (e.g. FC, etc.). Sinusoidal jitter is considered

to be a worst case jitter type.

Table 3-11. Receiver Total Jitter Tolerance Specification

Table 3-12. Periodic Receiver Jitter Tolerance Specification

RX-CID

V

V

V

V

T

Z

RL

1. This is the number of bits allowed without a transition on the incoming data stream when using DC coupling.

2. This is the typical number of bit times to re-lock to a new phase or frequency within +/- 300 ppm, assuming 8b10b encoded data.

3. AC coupling is used to interface to LVPECL and LVDS.

Deterministic

Random

Total

Deterministic

Random

Total

Deterministic

Random

Total

Deterministic

Random

Total

1. Values are measured with PRBS 2

2. Jitter specification is limited by measurement equipment capability.

Periodic

1. Values are measured with PRBS 2

2. Jitter specification is limited by measurement equipment capability.

RX-RELOCK

RX-TERM

RX-DIFF-S

RX-IN

RX-CM-DC

RX-CM-AC

Symbol

Description

Description

RX-RL

room temperature.

S

Stream of nontransitions

(CID = Consecutive Identical Digits) @ 10

Differential input sensitivity

Input levels

Input common mode range (DC coupled)

Input common mode range (AC coupled)

CDR re-lock time

Input termination 50/75 Ohm/High Z

Return loss (without package)

3.125 Gbps

2.5 Gbps

1.25 Gbps

250 Mbps

3.125 Gbps 600 mV differential eye

2.5 Gbps

1.25 Gbps

250 Mbps

Frequency

Frequency

2

2

2

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

600 mV differential eye

Description

7

7

-1, all channels operating, FPGA Logic active, I/Os around SERDES pins quiet, voltages are nominal,

-1, all channels operating.

1

Condition

Condition

3

-12

BER

3-40

1

Min.

Min.

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

Min.

100

0.5

—

—

—

0

0

DC and Switching Characteristics

LatticeECP2/M Family Data Sheet

Typ.

Typ.

7 @ 3.125 Gbps

20 @ 1.25 Gbps

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Typ.

50

—

—

—

—

—

9

Max.

Max.

0.54

0.26

0.60

0.80

0.61

0.22

0.81

0.53

0.22

0.80

0.42

0.10

0.20

0.22

0.20

0.08

V

CCRX

Max.

3000

1.2

1.5

—

—

+ 0.8

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

UI, p-p

Units

Units

mV, p-p

Ohms

Units

Bits

Bits

dB

V

V

V

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: