LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 95

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 95 of 385

- Download datasheet (3Mb)

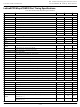

LatticeECP2/M sysCONFIG Port Timing Specifications

Lattice Semiconductor

sysCONFIG Byte Data Flow

t

t

t

t

t

t

t

t

t

sysCONFIG Byte Slave Clocking

t

t

t

sysCONFIG Serial (Bit) Data Flow

t

t

t

sysCONFIG Serial Slave Clocking

t

t

sysCONFIG POR, Initialization and Wake-up

t

t

t

t

t

t

t

t

t

t

sysCONFIG SPI Port

t

t

t

t

t

t

f

SUCBDI

HCBDI

CODO

SUCS

HCS

SUWD

HWD

DCB

CORD

BSCH

BSCL

BSCYC

SUSCDI

HSCDI

CODO

SSCH

SSCL

ICFG

VMC

PRGMRJ

PRGM

DINIT

DPPINIT

DPPDONE

IODISS

IOENSS

MWC

CFGX

CSSPI

CSCCLK

SOCDO

SOE

CSPID

MAXSPI

Parameter

Byte D[0:7] Setup Time to CCLK

Byte D[0:7] Hold Time to CCLK

CCLK to DOUT in Flowthrough Mode

CSN[0:1] Setup Time to CCLK

CSN[0:1] Hold Time to CCLK

Write Signal Setup Time to CCLK

Write Signal Hold Time to CCLK

CCLK to BUSY Delay Time

CCLK to Out for Read Data

Byte Slave CCLK Minimum High Pulse

Byte Slave CCLK Minimum Low Pulse

Byte Slave CCLK Cycle Time

DI Setup Time to CCLK Slave Mode

DI Hold Time to CCLK Slave Mode

CCLK to DOUT in Flowthrough Mode

Serial Slave CCLK Minimum High Pulse

Serial Slave CCLK Minimum Low Pulse

Minimum Vcc to INITN High

Time from t

PROGRAMN Pin Pulse Rejection

PROGRAMN Low Time to Start Configuration

PROGRAMN High to INITN High Delay

Delay Time from PROGRAMN Low to INITN Low

Delay Time from PROGRAMN Low to DONE Low

User I/O Disable from PROGRAMN Low

User I/O Enabled Time from CCLK Edge During Wake-up Sequence

Additional Wake Master Clock Signals after DONE Pin High

INITN High to CCLK Low

INITN High to CSSPIN Low

CCLK Low before CSSPIN Low

CCLK Low to Output Valid

CSSPIN[0:1] Active Setup Time

CSSPIN[0:1] Low to First CCLK Edge Setup Time

Max. CCLK Frequency - SPI Flash Read Opcode (0x03)

(SPIFASTN = 1)

Max. CCLK Frequency - SPI Flash Fast Read Opcode (0x0B)

(SPIFASTN = 0)

ICFG

to Valid Master CCLK

Over Recommended Operating Conditions

Description

3-44

DC and Switching Characteristics

LatticeECP2/M Family Data Sheet

300+3cyc

Min.

120

300

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

15

25

7

1

7

1

7

1

6

9

7

1

6

6

0

600+6cyc

Max.

28

50

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

12

12

12

12

37

37

35

25

15

20

2

8

1

1

2

cycles

Units

MHz

MHz

ms

ms

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

us

ns

ns

ns

ns

ns

ns

µs

us

ns

ns

ns

ns

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: