LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 49

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 49 of 385

- Download datasheet (3Mb)

Lattice Semiconductor

Each Transmit and Receive channel has its independent power supplies. The Output and Input buffers of each

channel also have their own independent power supplies. In addition, there are separate power supplies for PLL,

terminating resistor per quad.

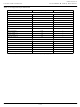

Figure 2-40. Simplified Channel Block Diagram for SERDES and PCS

PCS

As shown in Figure 2-40, the PCS receives the parallel digital data from the deserializer receivers and adjusts the

polarity, detects, byte boundary, decodes (8b/10b) and provides Clock Tolerance Compensation (CTC) FIFO for

changing the clock domain from receiver clock to the FPGA Clock.

For the transmit channel, the PCS block receives the parallel data from the FPGA core, encodes it with 8b/10b,

adjusts the polarity and passes the 8/10 bit data to the transmit SERDES channel.

The PCS also provides bypass modes that allow a direct 8-bit or 10-bit interface from the SERDES to the FPGA

logic. The PCS interface to FPGA can also be programmed to run at 1/2 speed for a 16-bit or 20-bit interface to the

FPGA logic.

SCI (SERDES Client Interface) Bus

The SERDES Client Interface (SCI) is a soft IP interface that allow the SERDES/PCS Quad block to be controlled

by registers as opposed to the configuration memory cells. It is a simple register configuration interface.

The ispLEVER design tools from Lattice support all modes of the PCS. Most modes are dedicated to applications

associated with a specific industry standard data protocol. Other more general purpose modes allow users to

define their own operation. With ispLEVER, the user can define the mode for each quad in a design.

Popular standards such as 10Gb Ethernet and x4 PCI-Express and 4x Serial RapidIO can be implemented using

IP (provided by Lattice), a single quad (Four SERDES channels and PCS) and some additional logic from the core.

For further information about SERDES, please see the list of additional technical documentation at the end of this

data sheet.

Receiver

SERDES (Analog)

Transmit

Equalizer

RX REFCLK

TX REFCLK

Serializer

TX PLL

8:1/10:1

Deserializer

1:8/1:10

Polarity

Polarity

PCS (Digital)

Adjust

Adjust

Recovered Clock

Byte Boundary

Detect, 8b/10b

Decoder

2-46

Encoder

8b/10b

CTC

FIFO

LatticeECP2/M Family Data Sheet

Sample

FIFO

Up

FPGA Receive Clock

FPGA Transmit Clock

Sample

Down

FIFO

From Transmit PLL

(In Common Block)

Transmit Data

8/10 bits or

16/20 bits

Elastic Buffer

Receive Data

Read Clock

16/20 bits

Architecture

To FPGA Core

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: