LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 44

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 44 of 385

- Download datasheet (3Mb)

Lattice Semiconductor

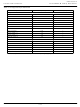

Figure 2-38. LatticeECP2M Banks

LatticeECP2/M devices contain two types of sysI/O buffer pairs.

1. Top (Bank 0 and Bank 1) sysI/O Buffer Pairs (Single-Ended Outputs Only)

2. Bottom (Bank 4 and Bank 5) sysI/O Buffer Pairs (Single-Ended Outputs Only)

The sysI/O buffer pairs in the top banks of the device consist of two single-ended output drivers and two sets of

single-ended input buffers (both ratioed and referenced). One of the referenced input buffers can also be con-

figured as a differential input.

The two pads in the pair are described as “true” and “comp”, where the true pad is associated with the positive

side of the differential input buffer and the comp (complementary) pad is associated with the negative side of

the differential input buffer.

The sysI/O buffer pairs in the bottom banks of the device consist of two single-ended output drivers and two

V

V REF1(7)

V REF2(7)

V CCIO6

V REF1(6)

V REF2(6)

CCIO7

GND

GND

SERDES

SERDES

Quad

Quad

Bank 0

Bank 5

BOTTOM

TOP

2-41

Bank 1

Bank 4

LatticeECP2/M Family Data Sheet

SERDES

SERDES

Quad

Quad

V CCIO2

V REF1(2)

V REF2(2)

V CCIO3

V REF1(3)

V REF2(3)

V CCIO8

GND

GND

GND

Architecture

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: