LFE2M20E-6FN256C LATTICE SEMICONDUCTOR, LFE2M20E-6FN256C Datasheet - Page 88

LFE2M20E-6FN256C

Manufacturer Part Number

LFE2M20E-6FN256C

Description

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer

LATTICE SEMICONDUCTOR

Series

LatticeECP2Mr

Datasheet

1.LFE2-12E-5FN256C.pdf

(385 pages)

Specifications of LFE2M20E-6FN256C

No. Of Logic Blocks

19000

No. Of Macrocells

10500

No. Of Speed Grades

6

No. Of I/o's

140

Clock Management

DLL, PLL

I/o Supply Voltage

3.465V

Total Ram Bits

1217Kbit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice

Quantity:

710

Company:

Part Number:

LFE2M20E-6FN256C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

LFE2M20E-6FN256C-5I

Manufacturer:

NATIONAL

Quantity:

633

- Current page: 88 of 385

- Download datasheet (3Mb)

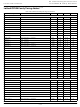

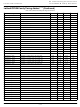

Lattice Semiconductor

DLL Timing

f

f

f

f

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

1. CLKOP runs at the same frequency as the input clock.

2. CLKOS minimum frequency is obtained with divide by 4.

3. This is intended to be a “path-matching” design guideline and is not a measurable specification.

Timing v.A 0.11

Parameter

REF

FB

CLKOP

CLKOS

PJIT

CYJIT

DUTY

DUTYTRD

DUTYCIR

SKEW

PWH

PWL

R

INSTB

LOCK

RSWD

PA

RANGE1

RANGE4

, t

F

3

1

2

Input reference clock frequency (on-chip or off-chip)

Feedback clock frequency (on-chip or off-chip)

Output clock frequency, CLKOP

Output clock frequency, CLKOS

Output clock period jitter (clean input)

Output clock cycle to cycle jitter (clean input)

Output clock duty cycle (at 50% levels, 50% duty cycle input clock,

50% duty cycle circuit turned off, time reference delay mode)

Output clock duty cycle (at 50% levels, arbitrary duty cycle input

clock, 50% duty cycle circuit enabled, time reference delay mode)

Output clock duty cycle (at 50% levels, arbitrary duty cycle input

clock, 50% duty cycle circuit enabled, clock injection removal

mode)

Output clock to clock skew between two outputs with the same

phase setting

Input clock minimum pulse width high (at 80% level)

Input clock minimum pulse width low (at 20% level)

Input clock rise and fall time (20% to 80% levels)

Input clock period jitter

DLL lock time

Digital reset minimum pulse width (at 80% level)

Delay step size

Max. delay setting for single delay block (144 taps)

Max. delay setting for four chained delay blocks

Over Recommended Operating Conditions

Description

3-37

DC and Switching Characteristics

LatticeECP2/M Family Data Sheet

18,500

2.376

9.504

Min.

16.5

100

100

100

750

750

25

35

40

40

—

—

—

3

Typ.

42

24

—

—

—

—

—

—

—

—

—

—

—

—

6

34.214

+/-250

8.553

Max.

59.4

500

500

500

500

250

250

100

65

60

60

—

—

—

—

1

ps p-p

ps p-p

cycles

Units

MHz

MHz

MHz

MHz

ps

ps

ps

ns

ps

ns

ps

ns

ns

%

%

%

Related parts for LFE2M20E-6FN256C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

IC, LATTICEECP2M FPGA, 420MHZ, FPBGA-256

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeECP2M Family 19000 Cells 90nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: