R8A77850ADBGV Renesas Electronics America, R8A77850ADBGV Datasheet - Page 1051

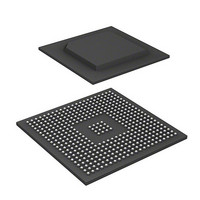

R8A77850ADBGV

Manufacturer Part Number

R8A77850ADBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ADBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ADBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Company:

Part Number:

R8A77850ADBGV#RD0Z

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1051 of 1694

- Download datasheet (9Mb)

20. Graphics Data Translation Accelerator (GDTA)

20.4.2

Explanation of MC Operation

By writing 1 to the MC_EN bit in GACER, registers in the MC register unit can be accessed.

After setting, as initial values, the input frame width/height, input YUV padding size, output frame

YUV pointer, past frame YUV pointer and future frame YUV pointer, data written in succession

to MCCF is received, and upon receiving a maximum of eight command parameters (estimating

mode, vector, buffer RAM 1 address), processing is begun. In processing, data is read in

macroblock units (Y: 16 pixels × 16 lines, U/V: 8 pixels × 8 lines), and estimated image

generation is performed within the module. The generated image by the amount of a macroblock

is output to the output destination.

The MC can store four commands (in register MCCF) and does not accept the command for the

next frame when four commands are already stored (command FIFO full). A judgment as to

whether processing has ended can be made by using either an interrupt or the MC_END bit in

GACISR.

Figure 20.6 illustrates the processing of one Y macroblock in "forward macroblock processing".

(After three rounds of processing for Y, U, and V have been done, a processing-end interrupt is

generated by writing an end command.) On the other hand, in "reverse macroblock processing" the

address for reading data from DDR2, shown in figure 20.6, is changed to the future frame pointer,

and other processing is the same. Hence in "bidirectional macroblock processing", (half-pixel-

corrected past data + half-pixel-corrected future data + 1)/2 is taken to be the correction processing

result, and calculation is performed with the IDCT data.

Finally, in "intra macroblock processing" signed IDCT data (the sign of which is discriminated

using the uppermost bit (bit 15)) is converted into unsigned 8-bit data and written to the output

position.

Rev.1.00 Jan. 10, 2008 Page 1019 of 1658

REJ09B0261-0100

Related parts for R8A77850ADBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: