R8A77850ADBGV Renesas Electronics America, R8A77850ADBGV Datasheet - Page 15

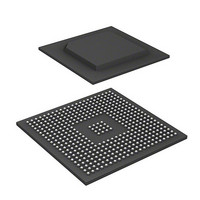

R8A77850ADBGV

Manufacturer Part Number

R8A77850ADBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ADBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ADBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Company:

Part Number:

R8A77850ADBGV#RD0Z

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 15 of 1694

- Download datasheet (9Mb)

8.7

8.8

Section 9 On-Chip Memory

9.1

9.2

9.3

9.4

9.5

9.6

Section 10 Interrupt Controller (INTC)

10.1 Features.............................................................................................................................. 263

10.2 Input/Output Pins ............................................................................................................... 272

10.3 Register Descriptions ......................................................................................................... 273

Store Queues ...................................................................................................................... 238

8.7.1

8.7.2

8.7.3

8.7.4

8.7.5

Notes on Using 32-Bit Address Extended Mode ............................................................... 241

Features.............................................................................................................................. 243

Register Descriptions ......................................................................................................... 246

9.2.1

9.2.2

9.2.3

9.2.4

9.2.5

Operation ........................................................................................................................... 256

9.3.1

9.3.2

9.3.3

9.3.4

On-Chip Memory Protective Functions ............................................................................. 260

Usage Notes ....................................................................................................................... 261

9.5.1

9.5.2

9.5.3

9.5.4

Note on Using 32-Bit Address Extended Mode................................................................. 262

10.1.1

10.1.2

10.3.1

10.3.2

10.3.3

10.3.4

10.3.5

SQ Configuration................................................................................................ 238

Writing to SQ...................................................................................................... 238

Transfer to External Memory.............................................................................. 239

Determination of SQ Access Exception.............................................................. 240

Reading from SQ ................................................................................................ 240

On-Chip Memory Control Register (RAMCR) .................................................. 247

OL memory Transfer Source Address Register 0 (LSA0).................................. 248

OL memory Transfer Source Address Register 1 (LSA1).................................. 250

OL memory Transfer Destination Address Register 0 (LDA0) .......................... 252

OL memory Transfer Destination Address Register 1 (LDA1) .......................... 254

Instruction Fetch Access from the CPU.............................................................. 256

Operand Access from the CPU and Access from the FPU ................................. 256

Access from the SuperHyway Bus Master Module ............................................ 257

OL Memory Block Transfer ............................................................................... 257

Page Conflict ...................................................................................................... 261

Access Across Different Pages ........................................................................... 261

On-Chip Memory Coherency ............................................................................. 261

Sleep Mode ......................................................................................................... 262

Interrupt Method................................................................................................. 266

Interrupt Sources................................................................................................. 267

External Interrupt Request Registers .................................................................. 277

User Mode Interrupt Disable Function ............................................................... 298

On-chip Module Interrupt Priority Registers ...................................................... 300

Individual On-Chip Module Interrupt Source Registers (INT2B0 to INT2B7).. 314

GPIO Interrupt Set Register (INT2GPIC) .......................................................... 322

.............................................................................................. 243

......................................................................... 263

Rev.1.00 Jan. 10, 2008 Page xiii of xxx

REJ09B0261-0100

Related parts for R8A77850ADBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: