CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 17

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

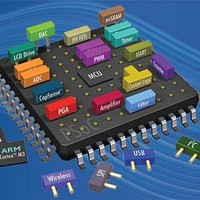

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is

repetitively read from system memory and written to a peripheral.

This is done with a single TD that chains to itself.

4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer

to be filled by one client while another client is consuming the

data previously received in the other buffer. In its simplest form,

this is done by chaining two TDs together so that each TD calls

the opposite TD when complete.

4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more

than two buffers. In this case there are multiple TDs; after the last

TD is complete it chains back to the first TD.

4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple

noncontiguous sources or destinations that are required to

effectively carry out an overall DMA transaction. For example, a

packet may need to be transmitted off of the device and the

packet elements, including the header, payload, and trailer, exist

in various noncontiguous locations in memory. Scatter gather

DMA allows the segments to be concatenated together by using

multiple TDs in a chain. The chain gathers the data from the

multiple locations. A similar concept applies for the reception of

data onto the device. Certain parts of the received data may need

to be scattered to various locations in memory for software

processing convenience. Each TD in the chain specifies the

location for each discrete element in the chain.

4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but

specifically refers to packet protocols. With these protocols,

there may be separate configuration, data, and status phases

associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped

configuration register can be written inside a peripheral,

specifying the overall length of the ensuing data phase. The CPU

can set up this configuration information anywhere in system

memory and copy it with a simple TD to the peripheral. After the

configuration phase, a data phase TD (or a series of data phase

TDs) can begin (potentially using scatter gather). When the data

Document Number: 001-11729 Rev. *R

phase TD(s) finish, a status phase TD can be invoked that reads

some memory mapped status information from the peripheral

and copies it to a location in system memory specified by the

CPU for later inspection. Multiple sets of configuration, data, and

status phase ‘subchains’ can be strung together to create larger

chains that transmit multiple packets in this way. A similar

concept exists in the opposite direction to receive the packets.

4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space

is memory mapped similar to any other peripheral. For example,

a first TD loads a second TD’s configuration and then calls the

second TD. The second TD moves data as required by the

application. When complete, the second TD calls the first TD,

which again updates the second TD’s configuration. This

process repeats as often as necessary.

4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware

resources to change program execution to a new address,

independent of the current task being executed by the main

code. The interrupt controller provides enhanced features not

found on original 8051 interrupt controllers:

Figure 4-2

interrupt triggered.

structure and priority polling.

Thirty-two interrupt vectors

Jumps directly to ISR anywhere in code space with dynamic

vector addresses

Multiple sources for each vector

Flexible interrupt to vector matching

Each interrupt vector is independently enabled or disabled

Each interrupt can be dynamically assigned one of eight

priorities

Eight level nestable interrupts

Multiple I/O interrupt vectors

Software can send interrupts

Software can clear pending interrupts

on page 18 represents typical flow of events when an

Figure 4-3

PSoC

®

on page 19 shows the interrupt

3: CY8C38 Family

Data Sheet

Page 17 of 129

[+] Feedback