CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 25

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

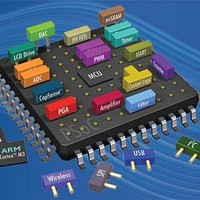

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

The extended data pointer SFRs, DPX0, DPX1, MXAX, and

P2AX, hold the most significant parts of memory addresses

during access to the xdata space. These SFRs are used only

with the MOVX instructions.

During a MOVX instruction using the DPTR0/DPTR1 register,

the most significant byte of the address is always equal to the

contents of DPX0/DPX1.

During a MOVX instruction using the R0 or R1 register, the most

significant byte of the address is always equal to the contents of

MXAX, and the next most significant byte is always equal to the

contents of P2AX.

I/O Port SFRs

The I/O ports provide digital input sensing, output drive, pin

interrupts, connectivity for analog inputs and outputs, LCD, and

access to peripherals through the DSI. Full information on I/O

ports is found in

I/O ports are linked to the CPU through the PHUB and are also

available in the SFRs. Using the SFRs allows faster access to a

limited set of I/O port registers, while using the PHUB allows boot

configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

Document Number: 001-11729 Rev. *R

INC DPTR

MOV DPTR, #data16

SFRPRTxDR sets the output data state of the port (where × is

port number and includes ports 0–6, 12 and 15).

The SFRPRTxSEL selects whether the PHUB PRTxDR

register or the SFRPRTxDR controls each pin’s output buffer

within the port. If a SFRPRTxSEL[y] bit is high, the

corresponding SFRPRTxDR[y] bit sets the output state for that

pin. If a SFRPRTxSEL[y] bit is low, the corresponding

PRTxDR[y] bit sets the output state of the pin (where y varies

from 0 to 7).

The SFRPRTxPS is a read only register that contains pin state

values of the port pins.

I/O System and Routing

on page 33.

5.7.3.1 xdata Space

The 8051 xdata space is 24-bit, or 16 MB in size. The majority of

this space is not ‘external’—it is used by on-chip components.

See

accessed using the EMIF. See

page 23.

Table 5-5. XDATA Data Address Map

0×00 0000 – 0×00 1FFF

0×00 4000 – 0×00 42FF

0×00 4300 – 0×00 43FF

0×00 4400 – 0×00 44FF

0×00 4500 – 0×00 45FF

0×00 4700 – 0×00 47FF

0×00 4900 – 0×00 49FF

0×00 4E00 – 0×00 4EFF

0×00 4F00 – 0×00 4FFF

0×00 5000 – 0×00 51FF

0×00 5400 – 0×00 54FF

0×00 5800 – 0×00 5FFF

0×00 6000 – 0×00 60FF

0×00 6400 – 0×00 6FFF

0×00 7000 – 0×00 7FFF

0×00 8000 – 0×00 8FFF

0×00 A000 – 0×00 A400

0×00 C000 – 0×00 C800

0×01 0000 – 0×01 FFFF

0×05 0220 – 0×05 02F0

0×08 0000 – 0×08 1FFF

0×80 0000 – 0×FF FFFF

Table

Address Range

5-5. External, that is, off-chip, memory can be

PSoC

SRAM

Clocking, PLLs, and oscillators

Power management

Interrupt controller

Ports interrupt control

Flash programming interface

I

Decimator

Fixed timer/counter/PWMs

I/O ports control

EMIF control registers

Analog subsystem interface

USB controller

UDB configuration

PHUB configuration

EEPROM

CAN

DFB

Digital Interconnect

configuration

Debug controller

Flash ECC bytes

External memory interface

®

2

External Memory Interface

C controller

3: CY8C38 Family

Purpose

Data Sheet

Page 25 of 129

on

[+] Feedback