CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 62

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

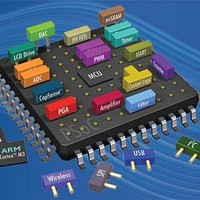

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

9.3 Debug Features

Using the JTAG or SWD interface, the CY8C38 supports the

following debug features:

9.4 Trace Features

The CY8C38 supports the following trace features when using

JTAG or SWD:

9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also

be used independently. SWV data is output on the JTAG

interface’s TDO pin. If using SWV, you must configure the device

for SWD, not JTAG. SWV is not supported with the JTAG

interface.

SWV is ideal for application debug where it is helpful for the

firmware to output data similar to 'printf' debugging on PCs. The

SWV is ideal for data monitoring, because it requires only a

single pin and can output data in standard UART format or

Manchester encoded format. For example, it can be used to tune

a PID control loop in which the output and graphing of the three

error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

9.6 Programming Features

The JTAG and SWD interfaces provide full programming

support. The entire device can be erased, programmed, and

verified. You can increase flash protection levels to protect

Document Number: 001-11729 Rev. *R

Halt and single-step the CPU

View and change CPU and peripheral registers, and RAM

addresses

Eight program address breakpoints

One memory access breakpoint—break on reading or writing

any memory address and data value

Break on a sequence of breakpoints (non recursive)

Debugging at the full speed of the CPU

Debug operations are possible while the device is reset, or in

low-power modes

Compatible with PSoC Creator and MiniProg3 programmer and

debugger

Standard JTAG programming and debugging interfaces make

CY8C38 compatible with other popular third-party tools (for

example, ARM / Keil)

Trace the 8051 program counter (PC), accumulator register

(ACC), and one SFR / 8051 core RAM register

Trace depth up to 1000 instructions if all registers are traced,

or 2000 instructions if only the PC is traced (on devices that

include trace memory)

Program address trigger to start tracing

Trace windowing, that is, only trace when the PC is within a

given range

Two modes for handling trace buffer full: continuous (overwriting

the oldest trace data) or break when trace buffer is full

32 virtual channels, each 32 bits long

Simple, efficient packing and serializing protocol

Supports standard UART format (N81)

firmware IP. Flash protection can only be reset after a full device

erase. Individual flash blocks can be erased, programmed, and

verified, if block security settings permit.

9.7 Device Security

PSoC 3 offers an advanced security feature called device

security, which permanently disables all test, programming, and

debug ports, protecting your application from external access.

The device security is activated by programming a 32-bit key

(0×50536F43) to a Write Once Latch (WOL).

The Write Once Latch is a type of nonvolatile latch (NVL). The

cell itself is an NVL with additional logic wrapped around it. Each

WOL device contains four bytes (32 bits) of data. The wrapper

outputs a ‘1’ if a super-majority (28 of 32) of its bits match a

pre-determined pattern (0×50536F43); it outputs a ‘0’ if this

majority is not reached. When the output is 1, the Write Once NV

latch locks the part out of Debug and Test modes; it also

permanently gates off the ability to erase or alter the contents of

the latch. Matching all bits is intentionally not required, so that

single (or few) bit failures do not deassert the WOL output. The

state of the NVL bits after wafer processing is truly random with

no tendency toward 1 or 0.

The WOL only locks the part after the correct 32-bit key

(0×50536F43) is loaded into the NVL's volatile memory,

programmed into the NVL's nonvolatile cells, and the part is

reset. The output of the WOL is only sampled on reset and used

to disable the access. This precaution prevents anyone from

reading, erasing, or altering the contents of the internal memory.

The user can write the key into the WOL to lock out external

access only if no flash protection is set (see

page 21). However, after setting the values in the WOL, a user

still has access to the part until it is reset. Therefore, a user can

write the key into the WOL, program the flash protection data,

and then reset the part to lock it.

If the device is protected with a WOL setting, Cypress cannot

perform failure analysis and, therefore, cannot accept RMAs

from customers. The WOL can be read out through the SWD port

to electrically identify protected parts. The user can write the key

in WOL to lock out external access only if no flash protection is

set. For more information on how to take full advantage of the

security features in PSoC see the PSoC 3 TRM.

Disclaimer

Note the following details of the flash code protection features on

Cypress devices.

Cypress products meet the specifications contained in their

particular Cypress data sheets. Cypress believes that its family

of products is one of the most secure families of its kind on the

market today, regardless of how they are used. There may be

methods, unknown to Cypress, that can breach the code

protection features. Any of these methods, to our knowledge,

would be dishonest and possibly illegal. Neither Cypress nor any

other semiconductor manufacturer can guarantee the security of

their code. Code protection does not mean that we are

guaranteeing the product as “unbreakable.”

Cypress is willing to work with the customer who is concerned

about the integrity of their code. Code protection is constantly

evolving. We at Cypress are committed to continuously

improving the code protection features of our products.

PSoC

®

3: CY8C38 Family

“Flash Security”

Data Sheet

Page 62 of 129

on

[+] Feedback