CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 38

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

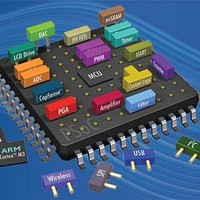

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

6.4.8 Analog Connections

These connections apply only to GPIO pins. All GPIO pins may

be used as analog inputs or outputs. The analog voltage present

on the pin must not exceed the Vddio supply voltage to which the

GPIO belongs. Each GPIO may connect to one of the analog

global busses or to one of the analog mux buses to connect any

pin to any internal analog resource such as ADC or comparators.

In addition, select pins provide direct connections to specific

analog features such as the high current DACs or uncommitted

opamps.

6.4.9 CapSense

This section applies only to GPIO pins. All GPIO pins may be

used to create CapSense buttons and sliders

“CapSense”

6.4.10 LCD Segment Drive

This section applies only to GPIO pins. All GPIO pins may be

used to generate Segment and Common drive signals for direct

glass drive of LCD glass. See the

page 58 for details.

6.4.11 Adjustable Output Level

This section applies only to SIO pins. SIO port pins support the

ability to provide a regulated high output level for interface to

external signals that are lower in voltage than the SIO’s

respective Vddio. SIO pins are individually configurable to output

either the standard Vddio level or the regulated output, which is

based on an internally generated reference. Typically a voltage

DAC (VDAC) is used to generate the reference (see

6-12). The

use and reference routing to the SIO pins. Resistive pullup and

pull-down drive modes are not available with SIO in regulated

output mode.

6.4.12 Adjustable Input Level

This section applies only to SIO pins. SIO pins by default support

the standard CMOS and LVTTL input levels but also support a

differential mode with programmable levels. SIO pins are

grouped into pairs. Each pair shares a reference generator block

which, is used to set the digital input buffer reference level for

interface to external signals that differ in voltage from Vddio. The

reference sets the pins voltage threshold for a high logic level

(see

Typically a voltage DAC (VDAC) generates the V

“DAC”

reference routing to the SIO pins.

Note

Document Number: 001-11729 Rev. *R

16. GPIOs with opamp outputs are not recommended for use with CapSense.

0.5 × Vddio

0.4 × Vddio

0.5 × V

V

REF

Figure

section on page 59 has more details on VDAC use and

REF

“DAC”

6-12). Available input thresholds are:

section on page 59 for more information.

section on page 59 has more details on VDAC

“LCD Direct Drive”

[16]

. See the

REF

section on

Figure

reference.

Figure 6-12. SIO Reference for Input and Output

6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level

feature of the SIOs as explained in the

section can be used to construct a comparator. The threshold for

the comparator is provided by the SIO's reference generator. The

reference generator has the option to set the analog signal

routed through the analog global line as threshold for the

comparator. Note that a pair of SIO pins share the same

threshold. The digital input path in

illustrates this functionality. In the figure, ‘Reference level’ is the

analog signal routed through the analog global. The hysteresis

feature can also be enabled for the input buffer of the SIO, which

increases noise immunity for the comparator.

6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support ‘hot swap’

capability to plug into an application without loading the signals

that are connected to the SIO pins even when no power is

applied to the PSoC device. This allows the unpowered PSoC to

maintain a high impedance load to the external device while also

preventing the PSoC from being powered through a GPIO pin’s

protection diode.

Input Path

Output Path

Output

Digital

Digital

Input

SIO_Ref

Drive

Logic

PSoC

Reference

Generator

®

Driver

Vhigh

3: CY8C38 Family

Voutref

Vinref

Figure 6-9

Adjustable Input Level

Data Sheet

on page 35

Page 38 of 129

PIN

[+] Feedback