CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 32

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

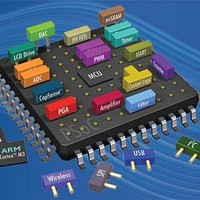

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

voltage. In standby mode, most boost functions are disabled,

thus reducing power consumption of the boost circuit. The

converter can be configured to provide low-power, low-current

regulation in the standby mode. The external 32-kHz crystal can

be used to generate inductor boost pulses on the rising and

falling edge of the clock when the output voltage is less than the

programmed value. This is called automatic thump mode (ATM).

The boost typically draws 200 µA in active mode and 12 µA in

standby mode. The boost operating modes must be used in

conjunction with chip power modes to minimize the total chip

power consumption.

available in different chip power modes.

Table 6-4. Chip and Boost Power Modes Compatibility

If the boost converter is not used in a given application, tie the

Vbat, Vssb, and Vboost pins to ground and leave the Ind pin

unconnected.

6.3 Reset

CY8C38 has multiple internal and external reset sources

available. The reset sources are:

Document Number: 001-11729 Rev. *R

Chip – Active mode

Chip – Sleep mode

Chip – Hibernate mode Boost can only be operated in active

Chip Power Modes

Power source monitoring – The analog and digital power

voltages, Vdda, Vddd, Vcca, and Vccd are monitored in several

different modes during power up, active mode, and sleep mode

(buzzing). If any of the voltages goes outside predetermined

ranges then a reset is generated. The monitors are

programmable to generate an interrupt to the processor under

certain conditions before reaching the reset thresholds.

External – The device can be reset from an external source by

pulling the reset pin (XRES) low. The XRES pin includes an

internal pull-up to Vddio1. Vddd, Vdda, and Vddio1 must all

have voltage applied before the part comes out of reset.

Watchdog timer – A watchdog timer monitors the execution of

instructions by the processor. If the watchdog timer is not reset

by firmware within a certain period of time, the watchdog timer

generates a reset.

Software – The device can be reset under program control.

Table 6-4

Boost can be operated in either active

or standby mode.

Boost can be operated in either active

or standby mode. However, it is recom-

mended to operate boost in standby

mode for low-power consumption

mode. However, it is recommended not

to use boost in chip hibernate mode

due to high current consumption in

boost active mode

lists the boost power modes

Boost Power Modes

Figure 6-7. Resets

The term device reset indicates that the processor as well as

analog and digital peripherals and registers are reset.

A reset status register holds the source of the most recent reset

or power voltage monitoring interrupt. The program may

examine this register to detect and report exception conditions.

This register is cleared after a power-on reset.

6.3.1 Reset Sources

6.3.1.1 Power Voltage Level Monitors

Reset

Pin

IPOR – Initial power-on reset

At initial power on, IPOR monitors the power voltages V

and V

corresponding internal regulators. The trip level is not precise.

It is set to approximately 1 volt, which is below the lowest

specified operating voltage but high enough for the internal

circuits to be reset and to hold their reset state. The monitor

generates a reset pulse that is at least 100 ns wide. It may be

much wider if one or more of the voltages ramps up slowly.

To save power the IPOR circuit is disabled when the internal

digital supply is stable. Voltage supervision is then handed off

to the precise low voltage reset (PRES) circuit. When the

voltage is high enough for PRES to release, the IMO starts.

PRES – Precise low voltage reset

This circuit monitors the outputs of the analog and digital

internal regulators after power up. The regulator outputs are

compared to a precise reference voltage. The response to a

PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the

digital PRES circuit. The analog regulator can be disabled,

which also disables the analog portion of the PRES. The PRES

circuit is disabled automatically during sleep and hibernate

modes, with one exception: During sleep mode the regulators

are periodically activated (buzzed) to provide supervisory

services and to reduce wakeup time. At these times the PRES

circuit is also buzzed to allow periodic voltage monitoring.

DDA

Vddd Vdda

Watchdog

Monitors

Software

External

Register

Voltage

, both directly at the pins and at the outputs of the

Power

Reset

Reset

Level

Timer

PSoC

Controller

®

Reset

3: CY8C38 Family

System

Processor

Reset

Data Sheet

Interrupt

Page 32 of 129

DDD

[+] Feedback