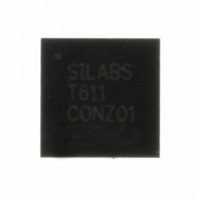

C8051T611-GM Silicon Laboratories Inc, C8051T611-GM Datasheet - Page 103

C8051T611-GM

Manufacturer Part Number

C8051T611-GM

Description

IC 8051 MCU 16K BYTE-PROG 28-QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051T61xr

Specifications of C8051T611-GM

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Program Memory Size

16KB (16K x 8)

Program Memory Type

OTP

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 17x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-QFN

Processor Series

C8051T6x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1.25 KB

Interface Type

I2C, SPI, UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

29

Number Of Timers

4

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051FT610DK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 21 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

336-1436-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051T611-GM

Manufacturer:

Silicon Labs

Quantity:

135

Company:

Part Number:

C8051T611-GMR

Manufacturer:

SILICON

Quantity:

3 500

Part Number:

C8051T611-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

SFR Definition 19.1. VDM0CN: V

SFR Address = 0xFF

19.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Assert-

ing an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST

pin may be necessary to avoid erroneous noise-induced resets. See Table 7.4 for complete RST pin spec-

ifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

19.4. Missing Clock Detector Reset

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system

clock remains high or low for more than the missing clock detector timeout, the one-shot will generate a

reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset

source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writ-

ing a 0 disables it. The state of the RST pin is unaffected by this reset.

Name

Reset

Bit

5:0

Type

7

6

Bit

VDDSTAT

VDMEN

Unused

VDMEN

Name

Varies

R/W

7

VDDSTAT

V

This bit turns the V

tem resets until it is also selected as a reset source in register RSTSRC (SFR Def-

inition 19.2). Selecting the V

may generate a system reset. In systems where this reset would be undesirable, a

delay should be introduced between enabling the V

reset source. See Table 7.4 for the minimum V

0: V

1: V

V

This bit indicates the current power supply status (V

0: V

1: V

Unused. Read = 000000b; Write = Don’t care.

Varies

DD

DD

R

6

DD

DD

DD

DD

Monitor Enable.

Status.

Monitor Disabled.

Monitor Enabled.

is at or below the V

is above the V

R

5

0

DD

DD

DD

monitor circuit on/off. The V

Monitor Control

monitor threshold.

DD

Rev 1.0

R

4

0

DD

monitor threshold.

monitor as a reset source before it has stabilized

C8051T610/1/2/3/4/5/6/7

Function

R

3

0

DD

DD

Monitor turn-on time.

R

2

0

DD

DD

Monitor cannot generate sys-

Monitor and selecting it as a

Monitor output).

R

1

0

R

0

0

103