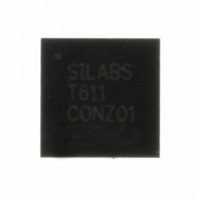

C8051T611-GM Silicon Laboratories Inc, C8051T611-GM Datasheet - Page 30

C8051T611-GM

Manufacturer Part Number

C8051T611-GM

Description

IC 8051 MCU 16K BYTE-PROG 28-QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051T61xr

Specifications of C8051T611-GM

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Program Memory Size

16KB (16K x 8)

Program Memory Type

OTP

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 17x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-QFN

Processor Series

C8051T6x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1.25 KB

Interface Type

I2C, SPI, UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

29

Number Of Timers

4

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051FT610DK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 21 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

336-1436-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051T611-GM

Manufacturer:

Silicon Labs

Quantity:

135

Company:

Part Number:

C8051T611-GMR

Manufacturer:

SILICON

Quantity:

3 500

Part Number:

C8051T611-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

C8051T610/1/2/3/4/5/6/7

30

Notes:

General

Solder Mask Design

Stencil Design

Card Assembly

Dimension

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. This Land Pattern Design is based on the IPC-7351 guidelines.

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder

4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used

5. The stencil thickness should be 0.125mm (5 mils).

6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

7. A 2x2 array of 1.10mm x 1.10mm openings on a 1.30mm pitch should be used for the center

8. A No-Clean, Type-3 solder paste is recommended.

9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for

C1

C2

X1

E

mask and the metal pad is to be 60m minimum, all the way around the pad.

to assure good solder paste release.

pad.

Small Body Components.

Figure 6.2. QFN-24 Recommended PCB Land Pattern

Table 6.2. QFN-24 PCB Land Pattern Dimesions

3.90

3.90

0.20

Min

0.50 BSC

Max

4.00

4.00

0.30

Rev 1.0

Dimension

X2

Y1

Y2

2.70

0.65

2.70

Min

Max

2.80

0.75

2.80