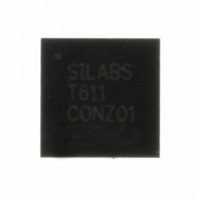

C8051T611-GM Silicon Laboratories Inc, C8051T611-GM Datasheet - Page 161

C8051T611-GM

Manufacturer Part Number

C8051T611-GM

Description

IC 8051 MCU 16K BYTE-PROG 28-QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051T61xr

Specifications of C8051T611-GM

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Program Memory Size

16KB (16K x 8)

Program Memory Type

OTP

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 17x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-QFN

Processor Series

C8051T6x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1.25 KB

Interface Type

I2C, SPI, UART

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

29

Number Of Timers

4

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051FT610DK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 21 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

336-1436-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051T611-GM

Manufacturer:

Silicon Labs

Quantity:

135

Company:

Part Number:

C8051T611-GMR

Manufacturer:

SILICON

Quantity:

3 500

Part Number:

C8051T611-GMR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not

used in this mode, and is not mapped to an external port pin through the crossbar. Since there is no way of

uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the

bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter

that determines when a full byte has been received. The bit counter can only be reset by disabling and re-

enabling SPI0 with the SPIEN bit. Figure 24.3 shows a connection diagram between a slave device in 3-

wire slave mode and a master device.

24.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to

logic 1:

All of the following bits must be cleared by software.

24.5. Serial Clock Phase and Polarity

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the

SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases

(edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low

clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0

should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The

clock and data line relationships for master mode are shown in Figure 24.5. For slave mode, the clock and

data relationships are shown in Figure 24.6 and Figure 24.7. Note that CKPHA should be set to 0 on both

the master and slave SPI when communicating between two Silicon Labs C8051 devices.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 24.3 controls the master mode

serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured

as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz,

whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for

full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-

wire slave mode), and the serial input data synchronously with the slave’s system clock. If the master

issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec)

must be less than 1/10 the system clock frequency. In the special case where the master only wants to

transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the

SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency.

This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave’s

system clock.

The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can

occur in all SPI0 modes.

The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when

the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to

SPI0DAT will be ignored, and the transmit buffer will not be written.This flag can occur in all SPI0

modes.

The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master, and for

multi-master mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN

bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a

transfer is completed and the receive buffer still holds an unread byte from a previous transfer. The new

byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The

data byte which caused the overrun is lost.

Rev 1.0

C8051T610/1/2/3/4/5/6/7

161