MC9S08DZ60MLC Freescale Semiconductor, MC9S08DZ60MLC Datasheet - Page 153

MC9S08DZ60MLC

Manufacturer Part Number

MC9S08DZ60MLC

Description

IC MCU 60K FLASH 4K RAM 32-LQFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Specifications of MC9S08DZ60MLC

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

CAN, I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

25

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 10x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

32-LQFP

For Use With

DEMO9S08DZ60 - BOARD DEMOEVB9S08DZ60 - BOARD EVAL FOR 9S08DZ60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08DZ60MLC

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 153 of 416

- Download datasheet (5Mb)

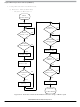

To change from FEI clock mode to FBI clock mode, follow this procedure:

8.5.2

When switching between operational modes of the MCG, certain configuration bits must be changed in

order to properly move from one mode to another. Each time any of these bits are changed (PLLS, IREFS,

CLKS, or EREFS), the corresponding bits in the MCGSC register (PLLST, IREFST, CLKST, or

OSCINIT) must be checked before moving on in the application software.

Additionally, care must be taken to ensure that the reference clock divider (RDIV) is set properly for the

mode being switched to. For instance, in PEE mode, if using a 4 MHz crystal, RDIV must be set to %001

(divide-by-2) or %010 (divide -by-4) in order to divide the external reference down to the required

frequency between 1 and 2 MHz.

The RDIV and IREFS bits should always be set properly before changing the PLLS bit so that the FLL or

PLL clock has an appropriate reference clock frequency to switch to.

Freescale Semiconductor

3. After the proper configuration bits have been set, wait for the affected bits in the MCGSC register

1. Change the CLKS bits to %01 so that the internal reference clock is selected as the system clock

2. Wait for the CLKST bits in the MCGSC register to change to %01, indicating that the internal

— If entering FEE, set RDIV appropriately, clear the IREFS bit to switch to the external reference,

— If entering FBE, clear the IREFS bit to switch to the external reference and change the CLKS

— The internal reference can optionally be kept running by setting the IRCLKEN bit. This is

to be changed appropriately, reflecting that the MCG has moved into the proper mode.

— If ERCLKEN was set in step 1 or the MCG is in FEE, FBE, PEE, PBE, or BLPE mode, and

— If in FEE mode, check to make sure the IREFST bit is cleared and the LOCK bit is set before

— If in FBE mode, check to make sure the IREFST bit is cleared, the LOCK bit is set, and the

source.

reference clock has been appropriately selected.

and leave the CLKS bits at %00 so that the output of the FLL is selected as the system clock

source.

bits to %10 so that the external reference clock is selected as the system clock source. The

RDIV bits should also be set appropriately here according to the external reference frequency

because although the FLL is bypassed, it is still on in FBE mode.

useful if the application will switch back and forth between internal and external modes. For

minimum power consumption, leave the internal reference disabled while in an external clock

mode.

EREFS was also set in step 1, wait here for the OSCINIT bit to become set indicating that the

external clock source has finished its initialization cycles and stabilized. Typical crystal startup

times are given in Appendix A, “Electrical Characteristics”.

moving on.

CLKST bits have changed to %10 indicating the external reference clock has been

appropriately selected. Although the FLL is bypassed in FBE mode, it is still on and will lock

in FBE mode.

MCG Mode Switching

MC9S08DZ60 Series Data Sheet, Rev. 4

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

153

Related parts for MC9S08DZ60MLC

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: