MC9S08DZ60MLC Freescale Semiconductor, MC9S08DZ60MLC Datasheet - Page 159

MC9S08DZ60MLC

Manufacturer Part Number

MC9S08DZ60MLC

Description

IC MCU 60K FLASH 4K RAM 32-LQFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Specifications of MC9S08DZ60MLC

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

CAN, I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

25

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 10x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

32-LQFP

For Use With

DEMO9S08DZ60 - BOARD DEMOEVB9S08DZ60 - BOARD EVAL FOR 9S08DZ60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08DZ60MLC

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 159 of 416

- Download datasheet (5Mb)

8.5.2.3

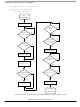

In this example, the MCG will move through the proper operational modes from BLPI mode at a 16 kHz

bus frequency running off of the internal reference clock (see previous example) to FEE mode using a 4

MHz crystal configured for a 16 MHz bus frequency. First, the code sequence will be described. Then a

flowchart will be included which illustrates the sequence.

Freescale Semiconductor

1. First, BLPI must transition to FBI mode.

2. Next, FBI will transition to FEE mode.

a) MCGC2 = 0x00 (%00000000)

b) Optionally, loop until LOCK (bit 6) in the MCGSC is set, indicating that the FLL has acquired

a) MCGC2 = 0x36 (%00110110)

b) Loop until OSCINIT (bit 1) in MCGSC is 1, indicating the crystal selected by the EREFS bit

c) MCGC1 = 0x38 (%00111000)

d) Loop until IREFST (bit 4) in MCGSC is 0, indicating the external reference clock is the current

e) Optionally, loop until LOCK (bit 6) in the MCGSC is set, indicating that the FLL has

f) Loop until CLKST (bits 3 and 2) in MCGSC are %00, indicating that the output of the FLL is

– LP (bit 3) in MCGSC is 0

lock. Although the FLL is bypassed in FBI mode, it is still enabled and running.

– RANGE (bit 5) set to 1 because the frequency of 4 MHz is within the high frequency range

– HGO (bit 4) set to 1 to configure external oscillator for high gain operation

– EREFS (bit 2) set to 1, because a crystal is being used

– ERCLKEN (bit 1) set to 1 to ensure the external reference clock is active

has been initialized.

– CLKS (bits 7 and 6) set to %00 in order to select the output of the FLL as system clock

– RDIV (bits 5-3) set to %111, or divide-by-128 because 4 MHz / 128 = 31.25 kHz which is

– IREFS (bit 1) cleared to 0, selecting the external reference clock

source for the reference clock

reacquired lock.

selected to feed MCGOUT

Example #3: Moving from BLPI to FEE Mode: External Crystal = 4 MHz,

Bus Frequency = 16 MHz

source

in the 31.25 kHz to 39.0625 kHz range required by the FLL

MC9S08DZ60 Series Data Sheet, Rev. 4

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

159

Related parts for MC9S08DZ60MLC

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: