R8A77850BDBGV#RD0Z Renesas Electronics America, R8A77850BDBGV#RD0Z Datasheet - Page 752

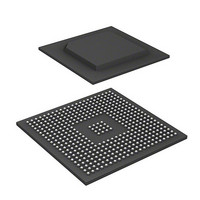

R8A77850BDBGV#RD0Z

Manufacturer Part Number

R8A77850BDBGV#RD0Z

Description

IC SUPERH MPU ROMLESS 436BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850BDBGV#RD0Z

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 752 of 1694

- Download datasheet (9Mb)

14. Direct Memory Access Controller (DMAC)

This function enables sequential voice compression by switching a storing buffer for data received

consequentially and a data buffer for processing signals alternately.

14.4.6

In a reload mode transfer, according to the settings of bits RPT in CHCR, the value set in

SARB/DARB is reloaded to SAR/DAR at each transfer set in bits 23 to 16 and bits 7 to 0 in

TCRB, and the transfer is repeated until TCR is 0 without specifying the transfer again. This

function is effective when data transfer with specific area is repeatedly executed. Figure 14.12

shows the operation of reload mode transfer.

In reload mode, TCRB is used as a reload counter. See section 14.3.6, DMA Transfer Count

Registers B0 to B3, B6 to B9 (TCRB0 to TCRB3, TCRB6 to TCRB9), and set TCRB.

Figure 14.12 shows an example of reload mode settings.

Rev.1.00 Jan. 10, 2008 Page 720 of 1658

REJ09B0261-0100

The relationship between the register settings and the source and destination addresses

of reload mode transfer is described below.

Register settings

DMA transfer source addresses and DMA transfer destination addresses in the above register settings

Set the source address in SAR (the data written to SAR is also written to SARB.)

Set the destination address in DAR

Set H'0000000C to TCR (12 transfers)

Set H'00040004 to TCRB (Reloading for every four transfers)

Set CHCR as follows.

Cycle 1:

Cycle 2:

Cycle 3:

Cycle 4:

Cycle 5:

Cycle 6:

Cycle 7:

Cycle 8:

Cycle 9:

Cycle 10: Source address = SAR + H'04

Cycle 11: Source address = SAR + H'08

Cycle 12: Source address = SAR + H'0C

RPT (bits 27 to 25) = B'111: Reload mode (Reloading SAR)

DM (bits 15 to 14) = B'01: An increase in DAR

SM (bits 13 to 12) = B'01: An increase in SAR

TS (bit 20 and bits 4 to 3) = B'010: Transfer for each (four-byte) longword

Reload Mode Transfer

Figure 14.12 Example of Operation Based on Reload Mode Settings

Source address = SAR

Source address = SAR + H'04

Source address = SAR + H'08

Source address = SAR + H'0C

Source address = SAR

Source address = SAR + H'04

Source address = SAR + H'08

Source address = SAR + H'0C

Source address = SAR

Destination address = DAR

Destination address = DAR + H'04

Destination address = DAR + H'08

Destination address = DAR + H'0C

Destination address = DAR + H'10 (reloading the value of SARB in SAR)

Destination address = DAR + H'14

Destination address = DAR + H'18

Destination address = DAR + H'1C

Destination address = DAR + H'20 (reloading the value of SARB in SAR)

Destination address = DAR + H'24

Destination address = DAR + H'28

Destination address = DAR + H'2C

Related parts for R8A77850BDBGV#RD0Z

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: