PSD935G2-90U STMicroelectronics, PSD935G2-90U Datasheet - Page 12

PSD935G2-90U

Manufacturer Part Number

PSD935G2-90U

Description

Manufacturer

STMicroelectronics

Datasheet

1.PSD935G2-90U.pdf

(91 pages)

Specifications of PSD935G2-90U

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Operating Temperature Classification

Commercial

Package Type

TQFP

Mounting

Surface Mount

Pin Count

80

Lead Free Status / RoHS Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PSD935G2-90U

Manufacturer:

STMicroelectronics

Quantity:

409

PSD935G2

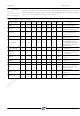

7.0 PSD935G2

Register

Description and

Address Offset

Table 6. Register Address Offset

Data In

Control

Data Out

Direction

Drive Select

Flash Protection

Flash Boot

Protection

PMMR0

PMMR2

Page

VM

Memory_ID0

Memory_ID1

Register Name

Port A Port B

06

00

04

08

Table 6 shows the offset addresses to the PSD935G2 registers relative to the CSIOP base

address. The CSIOP space is the 256 bytes of address that is allocated by the user to the

internal PSD935G2 registers. Table 6 provides brief descriptions of the registers in CSIOP

space. For a more detailed description, refer to section 9.

01

05

07

09

Port C

10

14

16

18

Port D Port E

11

15

17

19

30

32

34

36

38

Port F

40

42

44

46

Port G

41

43

45

47

49

Other*

C0

C2

B0

B4

E0

E2

F0

F1

PSD9XX Family

Reads Port pin as input,

MCU I/O input mode

Selects mode between

MCU I/O or Address Out

Stores data for output

to Port pins, MCU I/O

output mode

Configures Port pin as

input or output

Configures Port pins as

either CMOS or Open

Drain on some pins, while

selecting high slew rate

on other pins.

Read only – Flash Sector

Read only – PSD Security

Power Management

Register 0

Power Management

Register 2

Page Register

Places PSD memory

areas in Program and/or

Data space on an

individual basis.

Read only – Flash and

SRAM size

Read only – Boot type

and size

Protection

and Flash Boot Sector

Protection

Description

11