PSD935G2-90U STMicroelectronics, PSD935G2-90U Datasheet - Page 20

PSD935G2-90U

Manufacturer Part Number

PSD935G2-90U

Description

Manufacturer

STMicroelectronics

Datasheet

1.PSD935G2-90U.pdf

(91 pages)

Specifications of PSD935G2-90U

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Operating Temperature Classification

Commercial

Package Type

TQFP

Mounting

Surface Mount

Pin Count

80

Lead Free Status / RoHS Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PSD935G2-90U

Manufacturer:

STMicroelectronics

Quantity:

409

PSD935G2

The

PSD935G2

Functional

Blocks

(cont.)

9.1.1.5 Power-Up Condition

The PSD935G2 internal logic is reset upon power-up to the read array mode. The FSi and

CSBOOTi select signals, along with the write strobe signal, must be in the false state

during power-up for maximum security of the data contents and to remove the possibility of

data being written on the first edge of a write strobe signal. Any write cycle initiation is

locked when V

9.1.1.6 Read

Under typical conditions, the microcontroller may read the Flash, or secondary Flash

memories using read operations just as it would a ROM or RAM device. Alternately, the

microcontoller may use read operations to obtain status information about a program or

erase operation in progress. Lastly, the microcontroller may use instructions to read

special data from these memories. The following sections describe these read functions.

9.1.1.6.1 Read the Contents of Memory

Main Flash and secodary Flash memories are placed in the read array mode after

power-up, chip reset, or a Reset Flash instruction (see Table 8). The microcontroller can

read the memory contents of main Flash or secondary Flash by using read operations any

time the read operation is not part of an instruction sequence.

9.1.1.6.2 Read the Main Flash Memory Identifier

The main Flash memory identifier is read with an instruction composed of 4 operations:

3 specific write operations and a read operation (see Table 8). The PSD935G2 main Flash

memory ID is E8h.

9.1.1.6.3 Read the Flash Memory Sector Protection Status

The Flash memory sector protection status is read with an instruction composed of 4

operations: 3 specific write operations and a read operation (see Table 8). The read

operation will produce 01h if the Flash sector is protected, or 00h if the sector is not

protected.

The sector protection status for all NVM blocks (main Flash or secondary Flash) can also

be read by the microcontroller accessing the Flash Protection and Flash Boot Protection

registers in PSD I/O space. See section 9.1.1.9.1 for register definitions.

9.1.1.6.4 Read the Erase/Program Status Bits

The PSD935G2 provides several status bits to be used by the microcontroller to confirm

the completion of an erase or programming instruction of Flash memory. These status bits

minimize the time that the microcontroller spends performing these tasks and are defined

in Table 9. The status bits can be read as many times as needed.

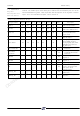

Table 9. Status Bits

NOTES: 1. X = Not guaranteed value, can be read either 1 or 0.

For Flash memory, the microcontroller can perform a read operation to obtain these status

bits while an erase or program instruction is being executed by the embedded algorithm.

See section 9.1.1.7 for details.

Flash

2. DQ7-DQ0 represent the Data Bus bits, D7-D0.

3. FSi/CSBOOTi are active high.

CSBOOTi

CC

FSi/

V

IH

is below VLKO.

Polling

Data

DQ7

Toggle

Flag

DQ6

Error

Flag

DQ5

DQ4

X

Erase

Time-

DQ3

out

PSD9XX Family

DQ2

X

DQ1

X

DQ0

X

19