PSD935G2-90U STMicroelectronics, PSD935G2-90U Datasheet - Page 13

PSD935G2-90U

Manufacturer Part Number

PSD935G2-90U

Description

Manufacturer

STMicroelectronics

Datasheet

1.PSD935G2-90U.pdf

(91 pages)

Specifications of PSD935G2-90U

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Operating Temperature Classification

Commercial

Package Type

TQFP

Mounting

Surface Mount

Pin Count

80

Lead Free Status / RoHS Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PSD935G2-90U

Manufacturer:

STMicroelectronics

Quantity:

409

8.0

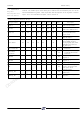

Register Bit

Definition

12

PSD9XX Family

Data In Registers – Port A, B, C, D, E, F and G

Data Out Registers – Port A, B, C, D, E, F and G

Direction Registers – Port A, B, C, D, E, F and G

Control Registers – Ports E, F and G

Drive Registers – Ports A, B, D, E, and G

Drive Registers – Ports C and F

Flash Protection Register

All the registers in the PSD935G2 are included here for reference. Detail description of the

registers are found in the Functional Block section of the Data Sheet.

Bit definitions:

Read only registers, read Port pin status when Port is in MCU I/O input Mode.

Bit definitions:

Latched data for output to Port pin when pin is configured in MCU I/O output mode.

Bit definitions:

Set Register Bit to 0 = configure corresponding Port pin in Input mode (default).

Set Register Bit to 1 = configure corresponding Port pin in Output mode.

Bit definitions:

Set Register Bit to 0 = configure corresponding Port pin in MCU I/O mode (default).

Set Register Bit to 1 = configure corresponding Port pin in Latched Address Out mode.

Bit definitions:

Set Register Bit to 0 = configure corresponding Port pin in CMOS output driver (default).

Set Register Bit to 1 = configure corresponding Port pin in Open Drain output driver.

Bit definitions:

Set Register Bit to 0 = configure corresponding Port pin as CMOS output driver (default).

Set Register Bit to 1 = configure corresponding Port pin in Slew Rate mode.

Bit definitions: Read Only Register

Sec<i>_Prot

Sec<i>_Prot

Port Pin 7

Sec7_Prot

Port Pin 7

Port Pin 7

Port Pin 7

Port Pin 7

Port Pin 7

Bit 7

Bit 7

Bit 7

Bit 7

Bit 7

Bit 7

Bit 7

Port Pin 6

Sec6_Prot Sec5_Prot Sec4_Prot

Port Pin 6

Port Pin 6

Port Pin 6

Port Pin 6

Port Pin 6

Bit 6

Bit 6

Bit 6

Bit 6

Bit 6

Bit 6

Bit 6

1 = Flash Sector <i> is write protected.

0 = Flash Sector <i> is not write protected.

Port Pin 5

Port Pin 5

Port Pin 5

Port Pin 5

Port Pin 5

Port Pin 5

Bit 5

Bit 5

Bit 5

Bit 5

Bit 5

Bit 5

Bit 5

Port Pin 4

Port Pin 4

Port Pin 4

Port Pin 4

Port Pin 4

Port Pin 4

Bit 4

Bit 4

Bit 4

Bit 4

Bit 4

Bit 4

Bit 4

Port Pin 3

Sec3_Prot Sec2_Prot Sec1_Prot Sec0_Prot

Port Pin 3

Port Pin 3

Port Pin 3

Port Pin 3

Port Pin 3

Bit 3

Bit 3

Bit 3

Bit 3

Bit 3

Bit 3

Bit 3

Port Pin 2

Port Pin 2

Port Pin 2

Port Pin 2

Port Pin 2

Port Pin 2

Bit 2

Bit 2

Bit 2

Bit 2

Bit 2

Bit 2

Bit 2

PSD935G2

Port Pin 1 Port Pin 0

Port Pin 1 Port Pin 0

Port Pin 1 Port Pin 0

Port Pin 1 Port Pin 0

Port Pin 1 Port Pin 0

Port Pin 1 Port Pin 0

Bit 1

Bit 1

Bit 1

Bit 1

Bit 1

Bit 1

Bit 1

Bit 0

Bit 0

Bit 0

Bit 0

Bit 0

Bit 0

Bit 0