PSD935G2-90U STMicroelectronics, PSD935G2-90U Datasheet - Page 18

PSD935G2-90U

Manufacturer Part Number

PSD935G2-90U

Description

Manufacturer

STMicroelectronics

Datasheet

1.PSD935G2-90U.pdf

(91 pages)

Specifications of PSD935G2-90U

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Operating Temperature Classification

Commercial

Package Type

TQFP

Mounting

Surface Mount

Pin Count

80

Lead Free Status / RoHS Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PSD935G2-90U

Manufacturer:

STMicroelectronics

Quantity:

409

PSD935G2

The

PSD935G2

Functional

Blocks

(cont.)

9.1.1.4 Memory Operation

The main Flash and secondary Flash memories are addressed through the microcontroller

interface on the PSD935G2 device. The microcontroller can access these memories in one

of two ways:

Typically, Flash memory can be read by the microcontroller using read operations, just

as it would read a ROM device. However, Flash memory can only be erased and

programmed with specific instructions. For example, the microcontroller cannot write a

single byte directly to Flash memory as one would write a byte to RAM. To program a byte

into Flash memory, the microcontroller must execute a program instruction sequence, then

test the status of the programming event. This status test is achieved by a read

operation or polling the Rdy/Busy pin (PE4).

The Flash memory can also be read by using special instructions to retrieve particular

Flash device information (sector protect status and ID).

9.1.1.4.1 Instructions

An instruction is defined as a sequence of specific operations. Each received byte is

sequentially decoded by the PSD and not executed as a standard write operation. The

instruction is executed when the correct number of bytes are properly received and the

time between two consecutive bytes is shorter than the time-out value. Some instructions

are structured to include read operations after the initial write operations.

The sequencing of any instruction must be followed exactly. Any invalid combination of

instruction bytes or time-out between two consecutive bytes while addressing Flash

memory will reset the device logic into a read array mode (Flash memory reads like a

ROM device).

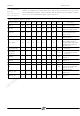

The PSD935G2 main Flash and secondary Flash support these instructions (see Table 8):

These instructions are detailed in Table 8. For efficient decoding of the instructions, the

first two bytes of an instruction are the coded cycles and are followed by a command byte

or confirmation byte. The coded cycles consist of writing the data AAh to address X555h

during the first cycle and data 55h to address XAAAh during the second cycle (unless the

Bypass Instruction feature is used. See 9.1.1.7). Address lines A15-A12 are don’t care

during the instruction write cycles. However, the appropriate sector select signal (FSi or

CSBOOTi) must be selected.

The main Flash and the secondary Flash Block have the same set of instructions (except

Read main Flash ID). The chip selects of the Flash memory will determine which Flash will

receive and execute the instruction. The main Flash is selected if any one of the FS0-7 is

active, and the secondary Flash Block is selected if any one of the CSBOOT0-3 is active.

The microcontroller can execute a typical bus write or read operation just as it would

if accessing a RAM or ROM device using standard bus cycles.

The microcontroller can execute a specific instruction that consists of several write

and read operations. This involves writing specific data patterns to special addresses

within the Flash to invoke an embedded algorithm. These instructions are summarized

in Table 8.

Erase memory by chip or sector

Suspend or resume sector erase

Program a byte

Reset to read array mode

Read Main Flash Identifier value

Read sector protection status

Bypass Instruction

PSD9XX Family

17