PSD935G2-90U STMicroelectronics, PSD935G2-90U Datasheet - Page 14

PSD935G2-90U

Manufacturer Part Number

PSD935G2-90U

Description

Manufacturer

STMicroelectronics

Datasheet

1.PSD935G2-90U.pdf

(91 pages)

Specifications of PSD935G2-90U

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Operating Temperature Classification

Commercial

Package Type

TQFP

Mounting

Surface Mount

Pin Count

80

Lead Free Status / RoHS Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PSD935G2-90U

Manufacturer:

STMicroelectronics

Quantity:

409

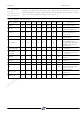

PSD935G2

8.0

Register Bit

Definition

(cont.)

Flash Boot Protection Register

Page Register

PMMR0 Register

PMMR2 Register

Bit definitions:

Sec<i>_Prot

Sec<i>_Prot

Security_Bit

Bit definitions:

Configure Page input to PLD. Default Pgr[7:0] = 00.

*

Bit definitions: (default is 0)

Bit 1 0 = Automatic Power Down (APD) is disabled.

Bit 3 0 = PLD Turbo is on.

Bit 4 0 = CLKIN input to the PLD AND array is connected.

Bit 5 0 = CLKIN input to the PLD Micro Cells is connected.

*

Bit definitions (defauld is 0):

Bit 0 0 = Address A[7:0] are connected into the PLD array.

Bit 2 0 = Cntl0 input to the PLD AND array is connected.

Bit 3 0 = Cntl1 input to the PLD AND array is connected.

Bit 4 0 = Cntl2 input to the PLD AND array is connected.

Bit 5 0 = Ale input to the PLD AND array is connected.

Bit 6 0 = DBE input to the PLD AND array is connected.

Security_Bit

Not used bit should be set to zero.

Not used bit should be set to zero.

Bit 7

Bit 7

Pgr7

Bit 7

Bit 7

*

*

1 = Automatic Power Down (APD) is enabled.

1 = PLD Turbo is off, saving power.

1 = CLKIN input to PLD AND array is disconnected, saving power.

1 = CLKIN input to the PLD Micro Cells is disconnected, saving power.

1 = Address A[7:0] are blocked from the PLD array, saving power.

1 = Cntl0 input to the PLD AND array is disconnected, saving power.

1 = Cntl1 input to the PLD AND array is disconnected, saving power.

1 = Cntl2 input to the PLD AND array is disconnected, saving power.

1 = Ale input to the PLD AND array is disconnected, saving power.

1 = DBE input to the PLD AND array is disconnected, saving power.

Every CLKIN change will power up the PLD when Turbo bit is off.

Note: in XA mode, A3-0 come from PF3-0 and A7-4 come from ADIO7-4.

array DBE

Bit 6

Bit 6

Pgr6

Bit 6

Bit 6

PLD

1 = Boot Block Sector <i> is write protected.

0 = Boot Block Sector <i> is not write protected.

0 = Security Bit in device has not been set.

1 = Security Bit in device has been set.

*

*

Mcells clk

array Ale

Bit 5

Bit 5

Pgr5

Bit 5

Bit 5

PLD

PLD

*

array Cntl2 array Cntl1 array Cntl0

array-clk

Bit 4

Bit 4

Pgr4

Bit 4

Bit 4

PLD

PLD

*

Sec3_Prot Sec2_Prot Sec1_Prot Sec0_Prot

Turbo

Bit 3

Bit 3

Pgr3

Bit 3

Bit 3

PLD

PLD

Bit 2

Bit 2

Pgr2

Bit 2

Bit 2

PLD

PSD9XX Family

*

enable

Bit 1

Bit 1

Pgr1

Bit 1

Bit 1

APD

*

array addr

Bit 0

Bit 0

Pgr0

Bit 0

Bit 0

PLD

*

13