20-668-0003 Rabbit Semiconductor, 20-668-0003 Datasheet - Page 122

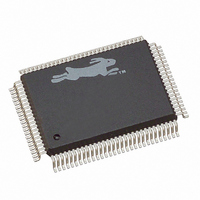

20-668-0003

Manufacturer Part Number

20-668-0003

Description

IC CPU RABBIT2000 30MHZ 100PQFP

Manufacturer

Rabbit Semiconductor

Datasheet

1.20-668-0003.pdf

(228 pages)

Specifications of 20-668-0003

Processor Type

Rabbit 2000 8-Bit

Speed

30MHz

Voltage

2.7V, 3V, 3.3V, 5V

Mounting Type

Surface Mount

Package / Case

100-MQFP, 100-PQFP

Data Bus Width

8 bit

Maximum Clock Frequency

30 MHz

Operating Supply Voltage

0 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Number Of Programmable I/os

40

Number Of Timers

8 & 10 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

20-668-0003

316-1062

316-1062

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

20-668-0003

Manufacturer:

Rabbit Semiconductor

Quantity:

10 000

- Current page: 122 of 228

- Download datasheet (2Mb)

The Timer B I/O registers are listed in Table 11-4.

The control/status register for Timer B (TBCSR) is laid out as shown in Table 11-5.

The control register for Timer B (TBCR) is laid out as shown in Table 11-6.

The MSB x registers for Timer B (TBM1R/TBM2R) are laid out as shown in Table 11-7.

116

Not used

Not used

Timer B Control/Status Register

Timer B Control Register

Timer B MSB 1 Reg

Timer B LSB 1 Reg

Timer B MSB 2 Reg

Timer B LSB 2 Reg

Timer B Count MSB Reg

Timer B Count LSB Reg

Bits 7:3

Table 11-5. Timer B Control and Status Register (TBCSR) (adr = 0x0B0)

Bits 7:4

Table 11-7. Timer B MSB x Register (TBM1R/TBM2R = 0x0B2/0x0B4)

Register Name

Two most significant bits of timer

match preload register.

1—A match with match

register 2 was detected.

This bit is cleared when

this register is read;

setting this bit to 1 enables

the interrupt.

00—Counter clocked by perclk/2

01—Counter clocked by output of timer A1

1x—Timer clocked by perclk/2 divided by 8

Table 11-6. Timer B Control Register (TBCR)

Bits 7:6

Bit 2

Table 11-4. Timer B Registers

Bits 3:2

TBCSR

TBCR

TBM1R

TBL1R

TBM2R

TBL2R

TBCMR

TBCLR

Mnemonic

Register

1—A match with match

register 1 was detected.

This bit is cleared when

this register is read;

setting this bit to 1 enables

the interrupt.

Not used.

Rabbit 2000 Microprocessor User’s Manual

Bit 1

B0

B1

B2

B3

B4

B5

BE

BF

Bits 5:0

Address

(hex)

00—Interrupt disabled

xx—Interrupt priority xx enabled.

I/O

1—Enable the main clock

for this timer.

R/W xxxxx000

W

W

W

W

R

R

R/W

Bits 1:0

xxxxxx00

x

x

x

x

x

x

Bit 0

On Reset

To

Related parts for 20-668-0003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC CPU RABBIT4000 128-LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

IC MPU RABIT3000A 55.5MHZ128LQFP

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

Microprocessors - MPU Rabbit 3000 TFBGA Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

Microprocessors - MPU Rabbit 4000 LQFP Microprocessor

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

IC, I/O EXPANDER, 8BIT, 40MHZ, TQFP-64

Manufacturer:

Rabbit Semiconductor

Part Number:

Description:

SCRs 1.5A 200uA 400V Sensing

Manufacturer:

Littelfuse Inc

Datasheet:

Part Number:

Description:

CARD 6-RELAY SMARTSTAR SR9500

Manufacturer:

Rabbit Semiconductor

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

ADAPTER 20 PIN .420" PLUGS(6PCS)

Manufacturer:

Logical Systems Inc.

Datasheet:

Part Number:

Description:

CONN BARRIER BLOCK .438" 20 POS

Manufacturer:

Cinch Connectors

Datasheet:

Part Number:

Description:

20 MODII 2PC HDR DR SHRD, ROHS

Manufacturer:

TE Connectivity

Datasheet:

Part Number:

Description:

WIRE-BOARD CONN RECEPTACLE, 6POS, 3.96MM

Manufacturer:

TE Connectivity

Datasheet: